# Silicon- and Graphene-based FETs for THz technology

Author Juan Antonio Delgado Notario

Supervisors Yahya Moubarak Meziani & Jesús Enrique Velázquez Pérez

> A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy in the Departamento de Física Aplicada at Universidad de Salamanca

A mi familia con cariño

#### Abstract

#### Silicon- and Graphene-based FETs for THz technology

This Thesis focuses on the study of the response to Terahertz (THz) electromagnetic radiation of different silicon substrate-compatible FETs. Strained-Si MODFETs, state-of-the-art FinFETs and graphene-FETs were studied.

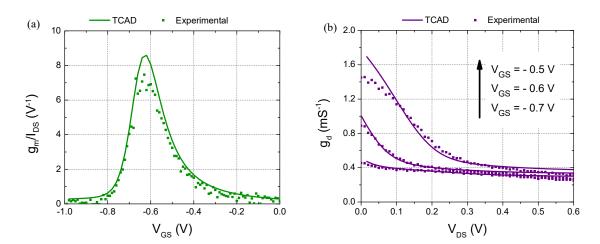

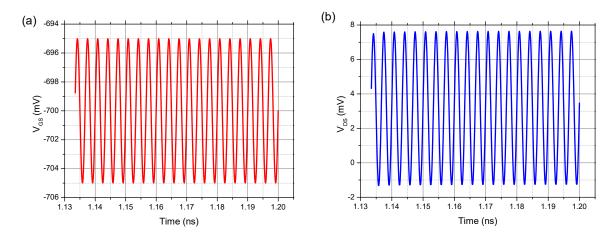

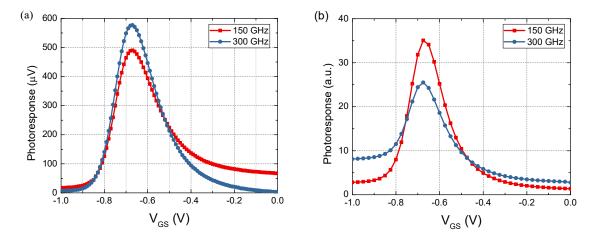

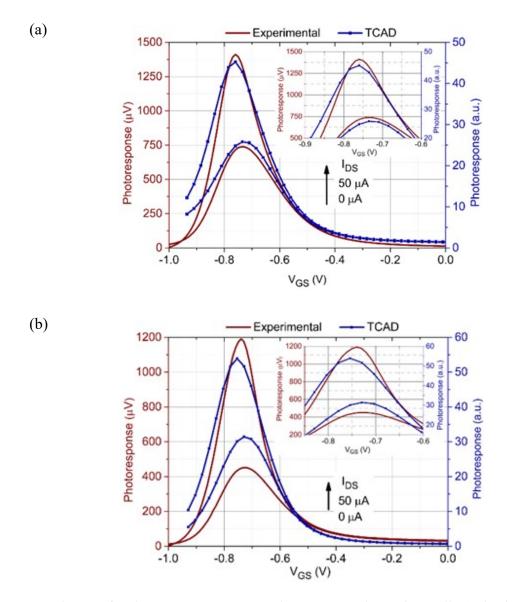

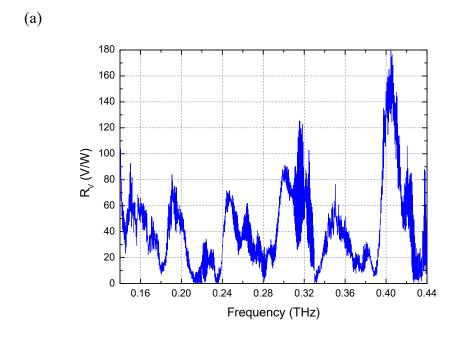

The first part of this thesis is devoted to present the results of an experimental and theoretical study of strained-Si MODFETs. These transistors are built by epitaxy of relaxed-SiGe on a conventional Si wafer to permit the fabrication of a strained-Si electron channel to obtain a high-mobility electron gas. Room temperature detection under excitation of 0.15 and 0.3 THz as well as sensitivity to the polarization of incoming radiations were demonstrated. A two-dimensional hydrodynamic-model was developed to conduct TCAD simulations to understand and predict the response of the transistors. Both experimental data and TCAD results were in good agreement demonstrating both the potential of TCAD as a tool for the design of future new THz devices and the excellent performance of strained-Si MODFETs as THz detectors (75 V/W and 0.06 nW/Hz<sup>0.5</sup>). The second part of the Thesis reports on an experimental study on the THz behavior of modern silicon FinFETs at room temperature. Silicon FinFETs were characterized in the frequency range 0.14-0.44 THz. The results obtained in this study show the potential of these devices as THz detectors in terms of their excellent Responsivity and NEP figures (0.66 kV/W and 0.05 nW/Hz<sup>0.5</sup>).

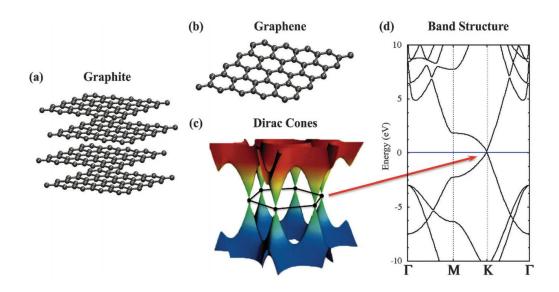

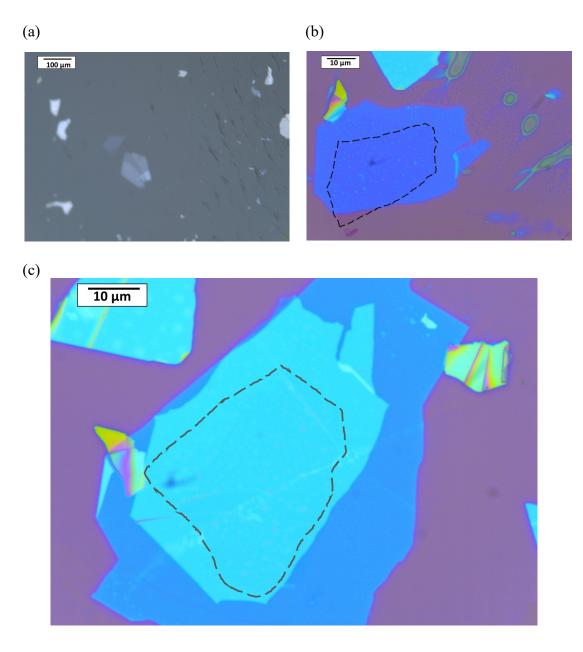

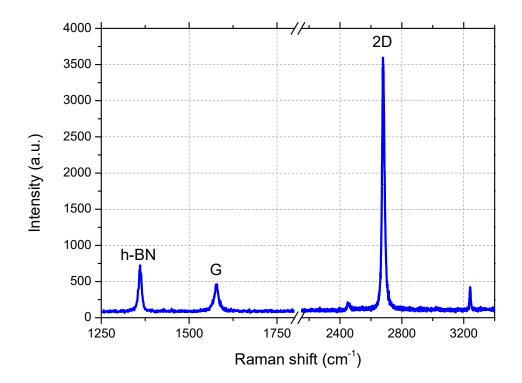

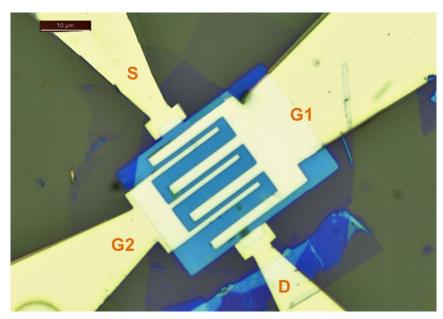

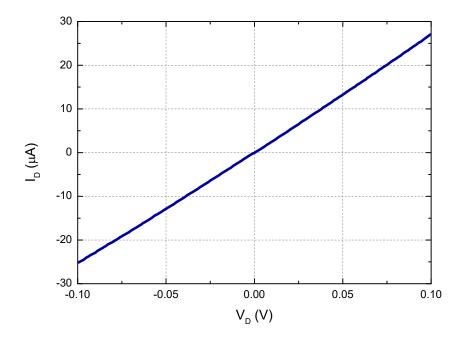

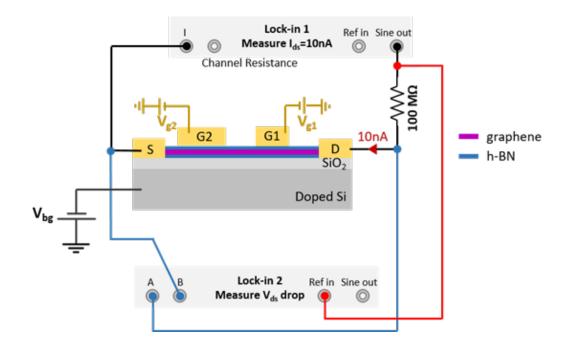

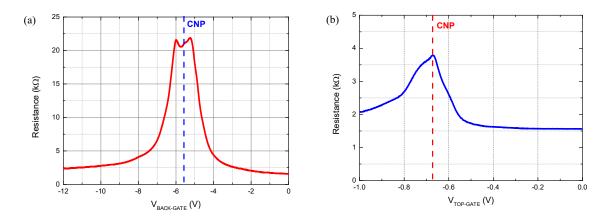

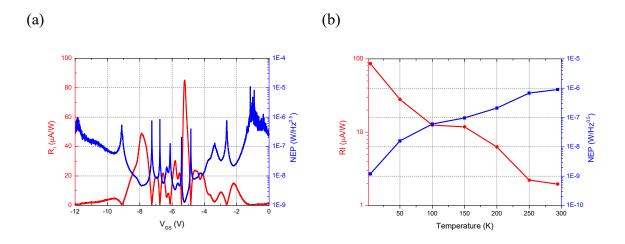

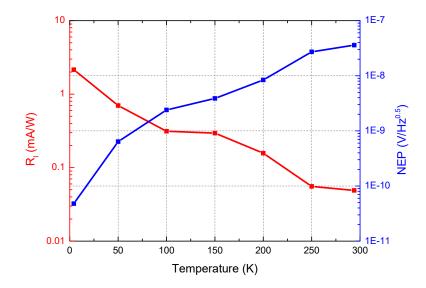

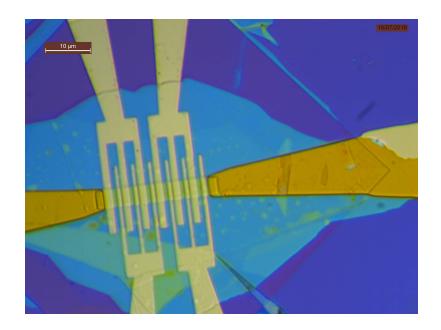

Finally, a large part of the Thesis is devoted to the fabrication and characterization of Graphene-based FETs. A novel transfer technique and an in-house-developed setup were implemented in the Nanotechnology Clean Room of the USAL and described in detail in this Thesis. The newly developed transfer technique enables to encapsulate a graphene layer between two flakes of h-BN. Raman measurements confirmed the quality of the fabricated graphene heterostructures and, thus, the excellent properties of encapsulated graphene. The asymmetric dual grating gate graphene FET (ADGG-GFET) concept was introduced as an efficient way to improve the graphene response to THz radiation. High quality ADGG-GFETs were fabricated and characterized under THz radiation. DC measurements confirmed the high quality of graphene heterostructures as it was shown on Raman measurements. A clear THz detection was found for both 0.15 THz and 0.3 THz at 4K when the device was voltage biased either using the back or the top gate of the G-FET. Room temperature THz detection was demonstrated at 0.3 THz using the ADGG-GFET. The device shows a Responsivity and NEP around 2.2 mA/W and 0.04 nW/Hz<sup>0.5</sup> respectively at respectively at 4K.

It was demonstrated the practical use of the studied devices for inspection of hidden objects by using the in-house developed THz imaging system.

**Key words**: THz, Plasma-waves, FETs, MODFETs, FinFETs, Silicon, Graphene.

### Acknowledgements

It is at the end of this PhD, when I am in front of my computer writing these lines and realizing how many people I am indebted to. Firstly, I would like to express my deepest gratitude to my supervisors Yahya and Jesús Enrique. I couldn't finish this thesis without the priceless help of both of you. My heartfelt thanks for accepting me as your student (firstly Master and then PhD student) for almost six years now and believe and trust in me throughout these years. Both of you taught me all I know about THz, carrying out countless experiments and simulations, encouraged me in those difficult times, gave me valuable lessons and advices, and in the meantime, you worried about me and my future. I am forever in your debt.

I would particularly like to thank to Enrique Diez for give me the opportunity to work into the Clean Room at USAL and opening me the door to the amazing *nanometric-world*. It was one of the biggest opportunities and challenges I ever faced, but, above all, it was a pleasure working with you and growing my experience. I would like to thank your never-ending support, faith and trusting me even in the darkest days when nothing seems to work in the Clean Room.

I would like to acknowledge Thomas Hackbarth (Daimler), who fabricated the strained-Si MODFETs and T. Chiarella, S. Demuynck and L. Ragnarsson whom fabricated the Silicon FinFETs, both of them used in this work. I also wish to thank Kristel Fobelets for her helpful collaborations on these projects.

Moschettieris, I am lucky meeting you and having friends like you. It was a pleasure working with all of you over the last years at the *IDi* (What is the *IDi*? :P), and of course all the coffees, talks, runnings, lunches and dinners. I really would had like to enjoy for a longer time, but it is time to conclude this Thesis. Adrian, Dani and Manu (Don Manuel), I wish to thank you for being helpful every time with all those hateful repairs, Clean Room cleanings and keeping that amazing learning spirit to lend a helping hand every time. Thank you because if I could fabricate the graphene devices or measure at the THz Lab it was largely because of you. David, I would like to thank you for so many experiences and lessons learned around the Raman spectrometer. Even if the situation was leading to that state commonly known as "triplete-excitado", your outstanding teaching and researcher spirits remained there to guide us. Yoann (or maybe it was Yuann), thank you because I could only remember you smiling despite the bad days or because nobody bought bread (it was funnier in Spanish). Your positive mindset was like a breath of fresh air during the year we match here in Salamanca. And finally, thanks to my colleague and friend Vito. It is really hard to summarize in few words the massive gratitude that you deserve. Thank you for standing by my side during those deadly and never-ending working days (even weekends or holidays), for facing and solving any problem we could find and because you taught me all I know about the Clean Room. This thesis would have not been finished without your priceless help. It is really hard combining a PhD with a Clean Room technician position (we both know), but it could not be possible without your massive support, encouragement, and that never-surrender spirit. You deserve the best and I hope *karma* will be fair with you soon in Salamanca.

During these years, I have had the pleasure to meet many friends. Maria, Vitor and Pilar, thank you for all the lunches and talks at the I+D+i and those attempts to recruit me as *tanguero*. Thank you Mamadou, for your help during those Clean Room cleaning days and because you could bring me out a smile always. Aurora, many thanks for passing me your happiness even in the worst days, for those comforting talks and for encouraging me in this final stretch. You were a second mom during this journey.

I would like to thank Wojciech Knap and Grzegorz Cywinsky for your hospitality and fruitful discussions during my stay in Warsaw. I would like to thank specially Dmytro But for your unstinting assistance and effort during the THz experiments and the lunches with those special bloody soups. Thanks also to Taiichi Otsuji sensei and Akira Satou sensei for your warm welcome, help and advice during my stay in Sendai. In particular, I would like to thank Arnold and Deepika for your help, not only during the experiments, but for those dinners, beers and experiences; both of you made me feel at home. *Arigato gozaimasu*!

Por último, pero no menos importante, a mi novia Irene y a mi familia: mi tío, mi abuela y mis padres: Perdón y gracias. Perdón porque soy consciente que, en este tramo final, el estrés, desanimo e irritación podía ser *el pan de cada día*, creando un aura a mi alrededor donde la solución más sencilla era no tratar conmigo. Sin embargo, siempre estuvisteis a mi lado durante todo este duro camino, aguantándome sin reprocharme nada, sacándome una sonrisa incluso en los momentos más difíciles, mostrando vuestra confianza y animándome en todo momento a pesar de que muchas veces (casi siempre) yo no contase nada y ello hiciese que no supieseis *a qué narices* me dedicaba. Os quiero!

.

### Table of contents

| ABSTRACT                                                  | V   |

|-----------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                          | VII |

| Introduction and motivation                               | 1   |

| 1. PLASMA-WAVE OSCILLATION IN A FET & TERAHERTZ DETECTION | 9   |

| 1.1 Analytic description                                  | 11  |

| 2. EXPERIMENTAL SETUP AND EQUIPMENT                       | 19  |

| 1.2 THz detection system from 4K up to 300K at USAL       |     |

| 1.3 THz detection & imaging system at USAL                |     |

| 1.4 THz detection & imaging system at USAL                |     |

| 1.5 Fabrication equipment                                 |     |

| 1.5.1 FE-SEM with Nanolithography Controller              |     |

| 1.6 Characterization equipment                            | 28  |

| 1.6.1 Profilometer                                        |     |

| 3. SILICON FETS                                           | 35  |

| 2.1 Introducción                                          | 37  |

| 2.2 Si/SiGe technology                                    | 37  |

| 2.2.1 Si, Ge and SiGe systems                             | 40  |

| 2.3 Strained-Si MODFETs                                   | 48  |

| 2.3.1 Introduction                                        |     |

| 2.4 Silicon FinFETs                                       | 73  |

| 2.4.1 Introduction                                        |     |

| 4. GRAPHENE FETS                                           | 85  |

|------------------------------------------------------------|-----|

| 3.1 Introduction                                           | 87  |

| 3.2 Graphene and Hexagonal Boron Nitride                   | 87  |

| 3.2.1 Graphene                                             | 87  |

| 3.2.2 Hexagonal Boron Nitride                              | 89  |

| 3.2.3 Graphene heterostructures                            |     |

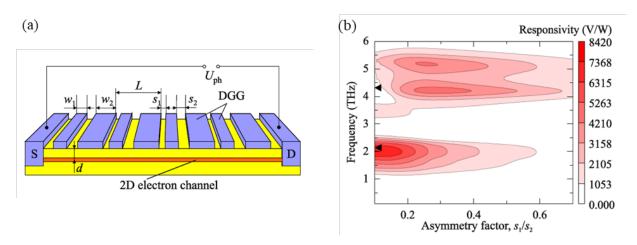

| 3.3 Asymmetric Dual Grating Gate                           | 91  |

| 3.4 Devices fabrication                                    | 93  |

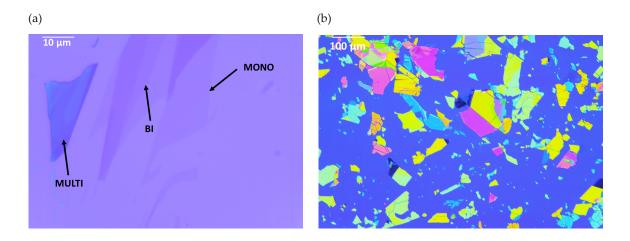

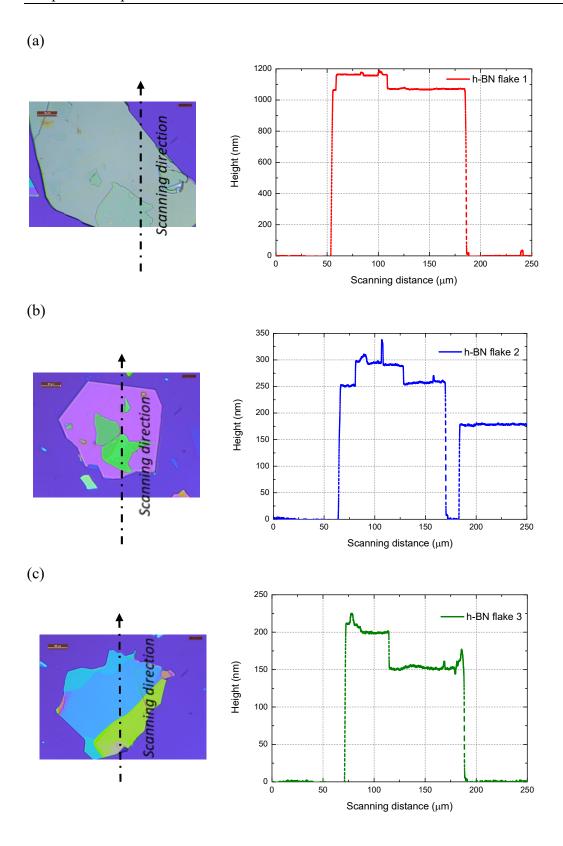

| 3.4.1 Graphene and h-BN production and characterization    | 93  |

| 3.4.2 Graphene heterostructures                            |     |

| 3.4.3 ADGG-GFETs fabrication process                       |     |

| 3.4.4 Fabrication troubleshooting                          |     |

| 3.4.5 Beyond ADGG-GFETs                                    | 117 |

| 3.5 Results and discussion                                 | 118 |

| 3.5.1 Electrical characterization at low temperature       | 119 |

| 3.5.2 THz detection measurements at low temperature        |     |

| 3.5.3 4K to Troom DC and THz detection measurements        |     |

| 3.5.4 Terahertz imaging with ADGG-GFET at Room temperature |     |

| 3.5.5 Responsivity and NEP                                 |     |

| 3.5.6 THz emission measurements                            | 139 |

| SUMMARY AND FUTURE WORK                                    | 143 |

| APPENDIX A: RESUMEN                                        | 147 |

| APPENDIX B: CONCLUSIONES Y PERSPECTIVAS                    | 149 |

| APPENDIX C: LIST OF PUBLICATIONS                           | 153 |

| BIBLIOGRAPHY                                               | 155 |

| FUNDING RECEIVED                                           | 167 |

### Introduction and motivation

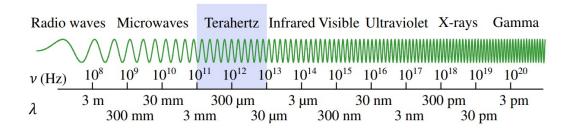

Terahertz (THz) rays are located in the spectral region between the microwave and the infrared portions of the electromagnetic spectrum (Fig. 0.1). While there is no a unique definition of the THz range, it is generally defined as the part of the EM spectrum from 0.1 to 10 THz, having respectively wavelengths from 3 mm down to 30  $\mu$ m (Figure 0.1). It covers the upper part of the millimeter waves spectral range (30-300 GHz), the whole range of submillimeter waves (0.3 to 3 THz) and the lower end part of the infrared range (3 to 10 THz).

Figure 0.1 THz range location on the Electromagnetic spectrum [1]

The THz region remains one of the most understudied range in the EM spectrum even though its potential applications in sensing, security, spectroscopy and communication are of big interest. The attractive features of THz radiation for applications are: (i) most packaging materials (such as paper or plastics) and cloths are transparent to this radiation [2] (ii) Many substances have "fingerprint" spectra in the THz range (iii) Due to its low photon energy (about one million times lower than the one of X-rays), THz radiation is non-ionizing and therefore not dangerous for human beings. The scientific interest in this field began in 1920 [3] and the term terahertz was first given by Fleming [4] in 1974. One of the first experiments on spectral content in the submillimeter range of interstellar medium was carried out by T.G. Philips and J. Keene in 1992 [5]. In the last decades a big interest was given to the development of terahertz devices for detection, emission, and mixing for different applications like: astronomy [6], spectroscopy (rotational, vibrational, and translational modes in the THz range are specific to a particular substance allowing to obtain a THz fingerprint) [7], [8], highly accurate thickness measurements of multilayered materials [9], communications with a bandwidth significantly higher than those based on microwaves [10], nondestructive inspection based on both imaging of concealed objects and spectroscopy [11], metrology [12], quality control [13], among others. THz rays (T-rays) permit imaging with a diffraction-limited resolution similar to that of the human eye [14], and, since common optically opaque packaging materials are transparent to T-rays, the inspection of concealed objects is possible. More interesting applications related to THz technology was reported in references [15], [16].

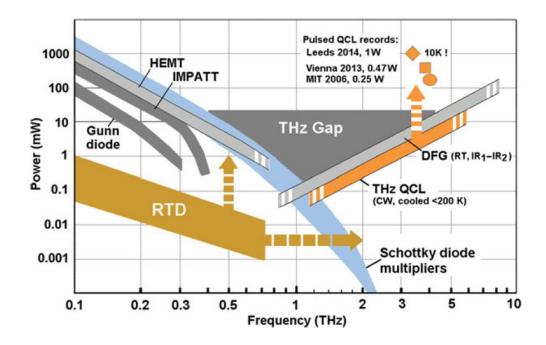

THz region is also known as "THz GAP" (Figure 0.2) since neither optical nor microwave devices could fully conquer this domain [17]. Then, an emphasis on the development of THz systems is needed. Although THz sensors and emitters have been significantly developed in the last decade, most of them are bulky and

expensive, which limits their application and availability and, therefore, there is a long way ahead on the development of THz devices.

Figure 0.2 Map of available compact terahertz sources. The "THz gap" indicates the central frequency interval in which is hard to generate any larger radiation power. (Abbreviations: QCL Quantum Cascade Laser, DFG Difference Frequency Generation, RTD Resonant Tunneling Diode, HEMT High Electron Mobility Transistor, IMPATT IMPact ionization Avalanche Transit Time diode, CW Continuous Wave, RT Room Temperature) [17]

One of the most promising ways to emit and/or detect THz is based on the oscillations of plasma wave in the channel of submicron Field Effect Transistors (FETs) as proposed theoretically by Dyakonov and Shur in 1993 [18] - [19]. Nevertheless, only FETs entirely implemented in silicon CMOS process technology keep all the advantages of cost-effectiveness, scalability, high yield and high reliability. Therefore, silicon-based FETs or, at least, silicon substrate compatible technologies are potential candidates to develop efficient and cheap THz devices that operate at room temperature.

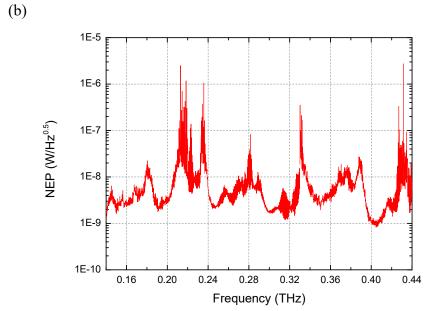

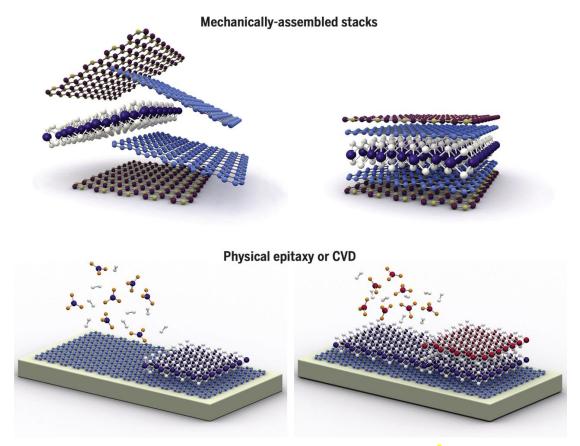

Since the first obtention of graphene flakes in 2004 [20], their excellent electronic and optical properties attracted interest to further investigate and develop room temperature graphene devices operating in the THz range that may contribute to close the THz GAP [21]. Moreover, new promising 2D materials also attract the interest to develop room-temperature THz devices. Nevertheless, it is well known that silicon dioxide (SiO<sub>2</sub>), the most common substrate material for graphene, limits the performance of graphene devices and obscures its performance. Recently, dielectric hexagonal boron nitride (h-BN) emerged as the ideal substrate for graphene because both materials share of the same type of lattice. Graphene is transferred on an h-BN flake to fabricate graphene based vertical heterostructures showing better properties than the conventional graphene on SiO<sub>2</sub>. One of the key advantages of 2D

materials and heterostructures is that they can be transferred to any substrate and therefore enables its integration in silicon integrated circuits.

In this Thesis, I focused my investigation line on the fabrication and characterization of different types of FETs (Si-based FET and Grpahene-based FETs) as THz detectors. This thesis manuscript was organized in four chapters as follow:

- Chapter 1 introduces the main mechanism of terahertz detection based on plasma-wave oscillations in the 2D channel of a FET. The theoretical model proposed by Dyakonov and Shur demonstrating that nanometric FETs can detect and emit THz radiation at frequencies above their cut-off frequency  $(f_t)$ , is recalled.

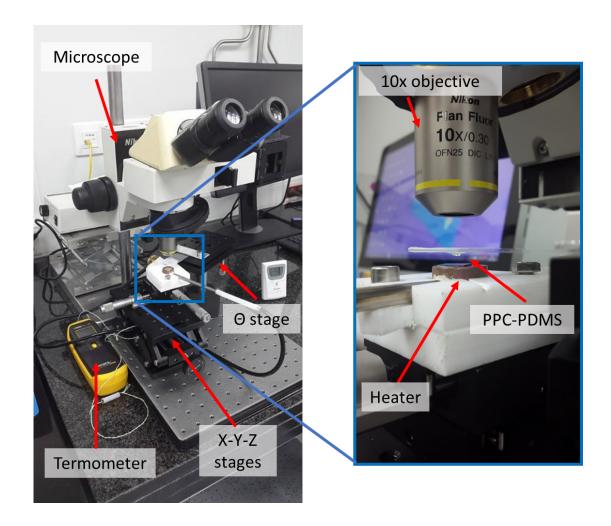

- Chapter 2 is dedicated to describe the experimental setups and equipment used for the fabrication of graphene-based FETs and the characterization of the transistors studied across this PhD work. An in-house e system developed in the PhD was used to transfer the graphene and h-BN flakes. Devices were characterized electrically on wafer using a probestation and/or wire bonded using gold wires to conduct further electrical measurements. Characterization was conducted both at room and at low (down to 4K) temperatures. THz characterizations at 0.15 & 0.3 THz were performed at room temperature using an original dual-use THz imaging system. THz low temperature measurements were also conducted. More experiments on detection at higher terahertz frequency and on emission of THz radiation were performed in collaboration with CEZAMAT (Warsaw, Poland) and RIEC, (Tohoku University, Japan).

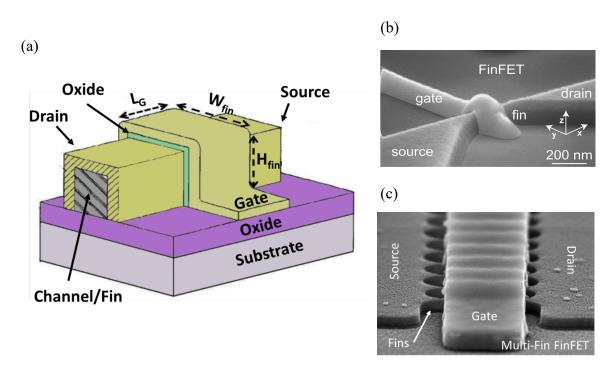

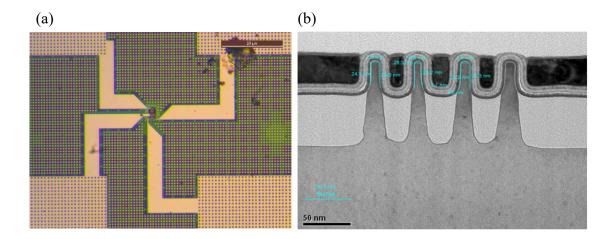

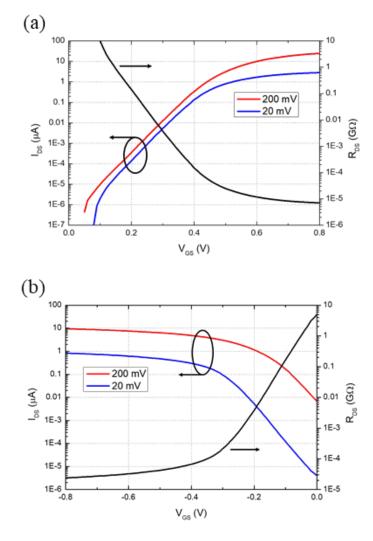

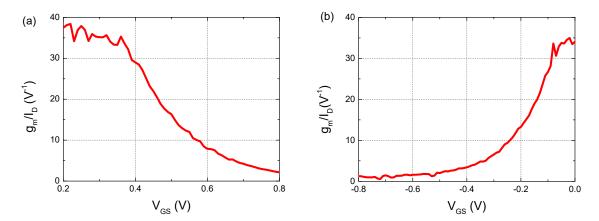

- Chapter 3: Two Si-based devices (Si-MODFET and FINFET) were experimentally studied in DC and as terahertz detectors. Strained-Si MODFETs were experimentally and theoretically characterized at 0.15 and 0.3 THz. A technology computer-aided design (TCAD) analysis based on a two-dimensional hydrodynamic model (HDM) was used to investigate the transistor response under THz radiation excitation. TCAD simulations were validated through comparison with experimental measurements carried at the THz Lab of USAL showing the potential of TCAD as a tool for the design of new THz devices. Moreover, both p-MOS and n-MOS silicon FinFETs were characterized on the THz range from 0.14 up to 0.44 THz at CEZAMAT laboratories (Warsaw, Poland). Both responsivity and Noise Equivalent Power (NEP) were extracted from measurement and show competitive values in comparison with other technologies. Terahertz imaging was performed to demonstrate the practical use of those devices for inspection applications.

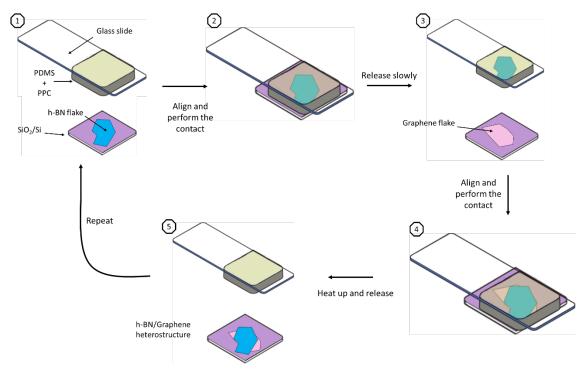

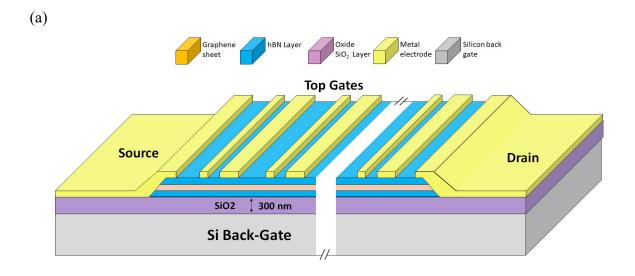

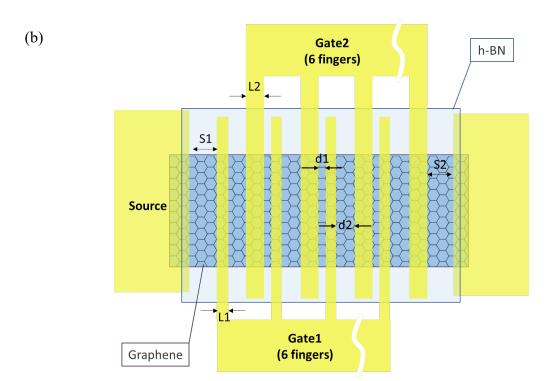

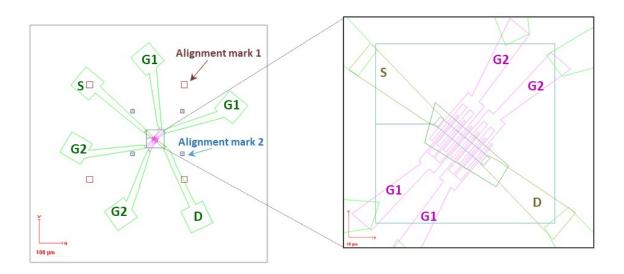

• Chapter 4 is dedicated to graphene-based FETs. An Asymmetric-Dual-Grating-Gate Graphene-based FET (ADGG-GFET) was proposed, fabricated, abd characterized as THz detector. The device was fabricated using a graphene heterostructure where the graphene flake was sandwiched between two layers of h-BN and then processed to fabricate a FET using an artificial double-heterostructure (h-BN/graphene/h-BN) on a Si O<sub>2</sub>/Si substrate. An experimental study from 4K up to room temperature was performed on the device as THz detector. Room temperature detection under 0.3 THz excitation was achieved and THz imaging was performed using the ADGG-GFET as the THz detector. Encouraging results using the ADGG-GFET for THz detection were obtained.

A conclusion of these works was presented at the final where all the obtained results were summarized. Moreover, as consequence of the promising results of the graphene-based devices, a future work plan will be presented as to continue the work of the presented thesis.

### Chapter 1

Plasma-Wave oscillation in a FET & Terahertz detection

#### 1.1 Analytic description

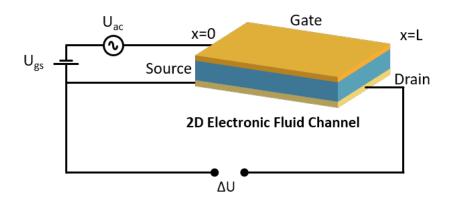

Dyakonov and Shur, first in 1993 [18] and later in 1996 [19], demonstrated theoretically the possibility of using submicron field-effect transistors (HEMTs, MOSFETs, ...) as practical device operating in the terahertz range to build detectors, multipliers and mixers. They found that the oscilation frequency of plasma waves in the channel of a gated 2D system (Figure 1.1) is inversely propotional to the gate length. Hence, a gated 2D system (FET) with submicron gate length could operate at frequencies well above their cut-off frequency (ft). When the electron plasma in the channel of a FET is excited by an external electromagnetic radiation, an AC electric field (Uac) is induced and converted to a measurable DC voltage, between drain and source, via a nonlinear mechanism. These devices present many advantages: low cost, small size, room temperature operation, high time response, and tuning the frequency by the gate voltage as compared to other devices used in THz technology.

**Figure 1.1** Schematic description of a FET operating as THz detector for an induced ac voltage

Figure 1.1 shows a schematic description of an ideal FET as a THz detector where a DC drain-to-source voltage ( $\Delta U$ ) appears as proportional to the incoming EM radiation. In an ideal case, the signal  $\Delta U$  should show a resonant dependence on the incoming radiation with maxima at the plasma oscilation frequency,  $\omega_0$ , and its odd harmonics  $\omega_N = (1+2N)\omega_0$ :

$$\omega_0 = \frac{\pi s}{2L} \tag{1.1}$$

where L is the transistor gate length and s is the plasma wave velocity that is given by the carriers' density and the gate-to-channel capacitance per unit area C:

$$s = \sqrt{\frac{e^2 n_s}{mC}} \tag{1.2}$$

e is the absolute value of the electron charge and m the electron mass. The carrier density in the FET channel is proportional to the gate swing or overdrive voltage  $(U_0)$  as:

$$n_s = \frac{CU_0}{e} \tag{1.3}$$

$U_0$ =  $V_G$ - $V_{th}$ ,  $V_G$  is the gate voltage and  $V_{th}$  the threshold voltage. Equation 1.3 only holds if the special variation of U(x) is larger than the gate-to-channel distance (gradual channel approximation). From those equations (1.1 to 1.3), an analytical expression can be obtained:

$$f_0 = \frac{1}{4} \sqrt{\frac{eU_0}{m}} \tag{1.4}$$

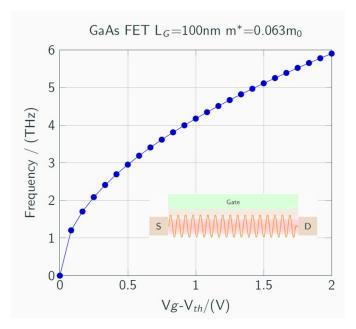

Figure 1.2 shows the resonance frequency versus  $U_0$  for a GaAs based FET with a gate legth of 100 nm. It shows that submicron FET devices could operate as a THz detector at room temperature and that the resonance frequency could be tuned by the gate bias.

**Figure 1.2** Resonance frequency as function of the gate voltage swing for a GaAs FET

The equations describing the 2D plasmons are the relationship between the surface carrier concentration  $(n_s)$  and the swing voltage  $(U_0)$  (Equation 1.2), the equation of motion (Euler equation, equation 1.5), and the continuity equation (Equation 1.6).

$$\frac{\partial U}{\partial t} + \frac{\partial (Uv)}{\partial x} = 0 \tag{1.5}$$

$$\frac{\partial v}{\partial t} = -\frac{e}{m} \frac{\partial U}{\partial x} - \frac{v}{\tau} \tag{1.6}$$

where  $\partial U/\partial x$  is the longitudinal electric field in the channel, v(x,t) is the local electron velocity, and the last term  $(v/\tau)$  describes the viscosity and accounts for electron collisions with phonons and/or impurities ( $\tau$  is the relaxation time). According to Dyakonov & Shur [18], [19] the solution of those equations under the boundary conditions of common-source and open-drain is given by:

$$\Delta U = \frac{U_a^2}{4U_o} f(\omega) \tag{1.7}$$

$$f(\omega) = 1 + \beta - \frac{1 + \beta \cos(2k_0'L)}{\sinh^2(k_0'L) + \cos^2(k_0'L)}$$

(1.8)

where:

$$\beta = \frac{2\omega\tau}{\sqrt{1 + (\omega\tau)^2}}\tag{1.9}$$

$$k_0' = \frac{\omega}{s} \sqrt{\frac{\left(1 + (\omega \tau)^{-2}\right)^{-1/2} + 1}{2}}$$

(1.10)

$$k_0'' = \frac{\omega}{s} \sqrt{\frac{\left(1 + \left(\omega\tau\right)^{-2}\right)^{-1/2} - 1}{2}}$$

(1.11)

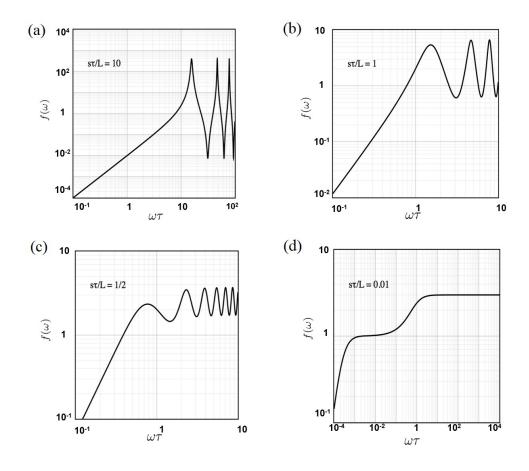

Equation 1.7 describes the response of the device as a THz detector for any frequency and gate length. The function  $f(\omega)$  depends on two dimensionless parameters:  $\omega \tau$  (quality factor) and  $s\tau/L$ . Figure 1.3 shows  $f(\omega)$  as a function of  $\omega \tau$  for different values of  $s\tau/L$ . When  $\omega\tau >> 1$  and for submicron devices, such that  $s\tau/L >> 1$ ,  $f(\omega)$ exhibits sharp resonances at the fundamental frequency and its odd harmonics (Figure 1.3 (a) and (b)). In this case, the damping of the plasma waves excited by the incoming radiation is small and the device exhibits a resonance detection mode. However, when  $\omega \tau$ << 1, plasma oscillations in the channel are overdamped. For a long device, the oscillations excited at the source by the incoming radiation do not reach the drain because of the damping. The boundary conditions at the drain are irrelevant in this case, and the response does not depend on L. As it can be seen in Figure 1(c) and (d),  $f(\omega)$  changes from  $f \sim 1$  for  $\omega \tau \ll 1$  to  $f \sim 3$  for  $\omega \tau \gg 1$ ; we also see how at very small values of  $\omega \tau$ the condition of a long sample is violated, and f tends to zero. In both cases, a long channel acts as a broadband detector of electromagnetic radiation. Underdamped  $(\omega\tau >> 1)$  or overdamped  $(\omega\tau >> 1)$  plasma waves decay near the source end of the channel, leading to a DC voltage induced between drain and source.

**Figure 1.3** Function  $f(\omega)$  as function of different values of  $s\tau/L$

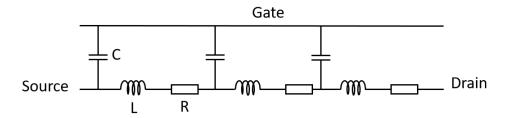

According to the simple analytical analysis presented in [22], an equivalent circuit of the FET can be given by a RLC ciruit as shown in Figure 1.4; where C is the capacitance gate-channel, R the channel resistance and L the kinetic inductance related to electron inertia that is proportional to the electron effective mass m. The operation of the FET as a THz detector will depend on the frequency  $\omega$ , the gate length L and the effective length  $L_{eff} = s\tau$  that describes the propagation distance of the waves inside the channel. Hence, it can be divided in two main regimes:

Figure 1.4 Equivalent circuit of FET when used as a detector

- 1. High frequency regime ( $\omega \tau > 1$ ), where  $\tau$  is again the electron momentum relaxation time, determining the conductivity in the channel  $\sigma$ =ne2C/m. In this case, the kinetic inductances in Figure 1.4 are of primordial importance, and the plasma waves analogous to the waves, in an RLC transmission line, will be excited.

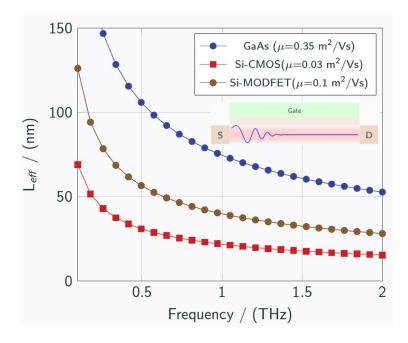

- a. For a short gate,  $L < L_{eff}$ , the plasma wave reaches the drain side of the channel, gets reflected, and forms a standing wave with an enhanced amplitude, in these conditions the channel acts as a resonant cavity for the waves. Figure 1.5 shows the dependence of  $L_{eff}$  with the frequency for different transistors (GaAs FET, Si-CMOS, and Si-MODFET). It is clearly seen that the effective length decreases when increasing the frequency and to reach the conditions for resonant detection, the gate length should be lower than  $L_{eff}$ . For example, for our studied transistors (Si-MODFET), the gate length should be less than 80nm at 0.3 THz.

- b. For a long gate, L>> $L_{eff}$ , the plasma waves excited at the source will decay before reaching the drain, so that the AC current will exist only in a small part of the channel adjacent to the source (inset of Figure 1.5).

- 2. Low frequency regime ( $\omega \tau << 1$ ), the plasma is overdamped and at this low frequency regime the impedance of the inductance is low. Hence, the inductance is in short-circuit and the equivalent circuit is mainly an RC circuit. The most relevant parameter is  $\omega \tau_{RC}$ , where  $\tau_{RC}$  is the RC time constant of the whole transistor. Since the total channel resistance is Lp/W, and the total capacitance is CWL (where W is the gate width and  $\rho=1/\sigma$  is the channel resistivity), it can be easily found that  $\tau_{RC}=L^2\rho C$ .

- a. For a short gate,  $\omega \tau_{RC} < 1$ , the AC current goes through the gate-to-channel capacitance uniformly across the whole length of the gate. This is the so-called "resistive mixer" regime [23], [24].

- b. For a long gate,  $\omega \tau_{RC} >> 1$ , the induced AC current will leak to the gate at a small distance l (leakage length) from the source, such that  $\tau_{RC} = l^2 \rho C$ . If l << L, then neither AC voltage nor AC current will exist in the channel at distances beyond l.

**Figure 1.5** Effective length as function of the frequency for GaAs, Si-CMOS and Si-MODFET.

In summary, resonant detection will be observed only if the quality factor is greater than unity and if the gate length of the FET is lower than the effective length given by st. In other cases, the detection is non-resonant, and the detector is a broadband one.

### Chapter 2

Experimental setup and equipment

This chapter describes the experimental setups used in DC and THz measurements from 4K to room temperature (T<sub>room</sub>) across this PhD work. Mainly, I have to mainly distinguish between two setups: the low temperature and THz measurements and imaging setup at USAL (University of Salamanca) premises and the THz detection setup at room temperature at CEZAMAT (Centre for Advanced Materials and Technologies, Warsaw, Poland) facilities. Additionally, a brief description of the experimental equipment for detection experiments is described.

Finnally, this chapter will describe the main equipment used for the characterization and fabrication of GFETs in this thesis.

## 1.2 THz detection system from 4K up to 300K at USAL

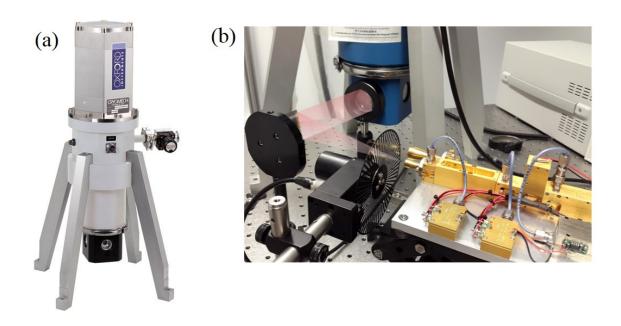

This section describes the setup used for DC and THz measurements in the temperature range 4K - 300K. An Optistat AC-V12 cryostat (Figure 2.1) cooled by a closed cycle refrigerator was used. This system is able to cool samples to helium temperatures without the need for liquid cryogens.

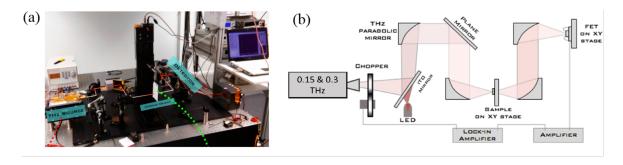

**Figure 2.1** Optical cryostat (a) and experimental setup (b) at USAL facilities for measurements in the range from 4K up to 300K.

The cryostat has 4 optical windows, each of them with a diameter of 12.7 mm that are used for the optical access. One of these optical windows was removed and replaced by a Teflon optical window to perform THz measurements and improve our THz setup. Teflon windows ensure that the sample is only excited by the THz radiation, since they

show good transmittances on these frequency ranges making them ideal components for IR and THz applications. Conversely, they exhibit close to zero transmittance in the visible range [25] ensuring that the devices are only excited by the incoming THz radiation. The samples placed on this system are held in vacuum and cooled by a Pulse Tube refrigerator. A temperature controller is used to control heating and thermometry of the sample from 4K up to 325K with a temperature stability of  $\pm 0.3K$ .

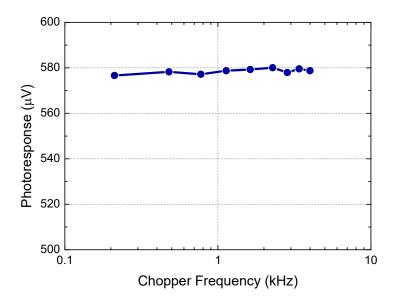

In THz experiments, transistors were excited by a RPG (Radiometer Physics GmbH) dual-frequency THz source. It uses a solid-state Dielectric Resonator Oscillator (DRO) at 12.5 GHz and electronic multiplication to generate a THz beam at 0.15 THz with an output power of 3 mW and another one at 0.3 THz with an output power of 6 mW. The output power was measured close to the source using a highly sensitive calibrated pyroelectric detector. For lock-in detection the THz radiation was modulated by a mechanical chopper between 0.1 and 4 kHz and then collimated and focused using an off-axis parabolic mirror and an optical lens.

Figure 2.1 (b) shows a photograph of the experimental bench described above. Since the sample is mechanically fixed into the cryostat it cannot be repositioned, rotated, or tilted, then the THz detection measurements performed on this system were limited. Nevertheless, the source was placed on a XYZ stage manipulator ensuring a proper alignment between the sample and the THz beam.

#### 1.3 THz detection & imaging system at USAL

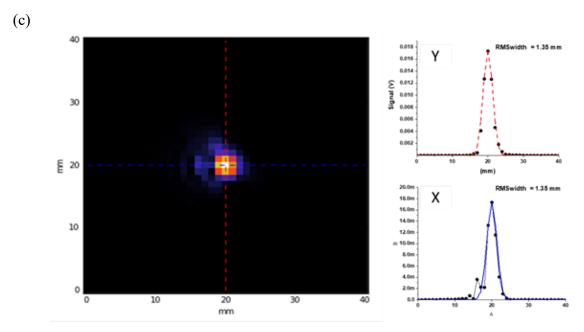

DC and THz measurements at room temperature performed at the THz Laboratory of the USAL were carried out in an additional optical bench. Figure 2.2 shows a photograph of this bench, (a), along with a scheme of the experimental setup used for the terahertz characterization at room temperature, (b). The DRO-based THz source and the mechanical chopper described in section 2.1. were both used in this system. The output THz radiation was modulated, collimated and focused twice by using an indium tin oxide (ITO) mirror and off-axis parabolic and plane mirrors. The ITO mirror acts as a dichroic mirror since the ITO layer is highly reflective (95%) for the THz beam due to its high conductivity while is highly transparent (80% transmittance) to visible light. This allows the use of a visible red LED (or laser) for the alignment of the THz beam. This experimental setup has two focal points. The second focal point (FP2) is used to place the THz detectors on a XYZ $\theta$  stage micromanipulator. Optionally, the system has a first focal point (FP1) to place an object that can be moved by using a XY stage. In this configuration, the incoming THz radiation goes through the object placed at FP1 and then the transmitted light is focused again at FP2 and measured with the THz detector using the lock-in amplifier. This configuration allows us to generate a pixel-by-pixel THz photograph of the object placed at FP1.

Figure 2.2 Photograph of the experimental bench, (a), schematic, (b) of the THz imaging setup implemented at the USAL Thz Lab, and image of the 0.3 THz beam and its shape profile (c).

The beam power and the spot area of the 0.15 and 0.3 THz EM radiation were measured using a calibrated pyroelectric detector at the FET position (FP2). Power values obtained were 0.5 mW at 0.15 THz and 1 mW at 0.3 THz. The spot area was estimated by taking a pixel-by-pixel image of the beam spot at the FET position. Figure 2.2 (c) shows a homogeneous circular beam spot for the 0.3 THz radiation. A similar shape was obtained for the 0.15 THz beam. The area of the beam spot was estimated to have a size of  $\pi r^2$ , where r is the radius of the beam spot. Values of 1.35 mm for 0.3 THz and 3.3 mm for 0.15 THz were found for r (Figure 2.2 (c) right).

# 1.4 THz detection & imaging system at USAL

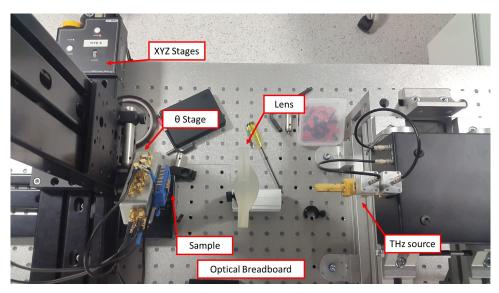

Broadband THz measurements at room temperature were performed at CEZAMAT facilities. Figure 2.3 shows a picture of the experimental setup used in the detection experiments carried out at this laboratory. The experimental setup comprised a THz-wave generator from VDI (Virginia Diodes, Inc.) and three Signal Generator Extension Modules offering full waveguide band coverage from 0.140 THz to 0.440 THz:

- WR5.1 140 220 GHz (typ. +4 dBm)

- WR3.4 220 330 GHz (typ. -2 dBm)

- WR2.2 330 440 GHz (typ. -10 dBm)

Figure 2.3 Photograph of the experimental bench at CEZAMAT facilities

The vertically polarized output THz beam was focalized on the devices placed at the focal point of the setup by using biconvex polyester/Teflon lenses. Devices were placed on a holder box fixed to  $XYZ\theta$  stages micromanipulators allowing us to perform measurements dependent on the beam polarization.

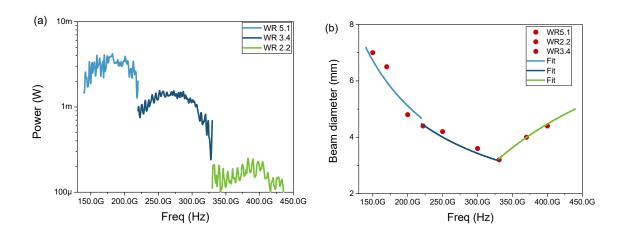

**Figure 2.4** Source power (a) and beam diameter (b) as a function of the output frequency in the frequency range from 0.15 up to 0.44 THz.

Figure 2.4 (a) shows the output power while the THz generator was tuned across the full frequency range of the system (140 - 440 GHz). The signal power was measured at the focal point by using a calibrated pyroelectric detector. Since the frequency was tuned, the beam diameter of the THz radiation changes across the frequency range. Its size was again measured at different frequencies (red dots - Figure 2.4 (b)) by taking a XY pixel-by-pixel image of the beam spot around the focal point. Then, different fits were performed for the different frequency ranges measurements to estimate the beam diameter across the full range (Figure 2.4 (b)).

# 1.5 Fabrication equipment

This section describes the equipment used for the fabrication of the ADGG-GFETs. The equipment is located into the Nanotechnology Clean Room of the USAL.

## 1.5.1 FE-SEM with Nanolithography Controller

Electron beam lithography processes were performed using a Scanning Electron Microscope (SEM) FE-SEM SIGMA FROM Zeiss with a nanolithography controller (Figure 2.5). The Zeiss Sigma is a SEM with a Schottky Field Emission (FE) source and a GEMINI electron optical column. The instrument has 2 detectors, an In-Lens Secondary Electron detector, lateral Secondary Electron (SE) Detector. Apertures range from 7.5 up to 120 microns and a maximum accelerating voltage of 15kV. The instrument includes 4-axis  $(x, y, z, \theta)$  fully motorized rotary stages. Samples of size as large as 20 cm are allowed.

Figure 2.5 Lithography system at USAL cleanroom

# 1.5.2 PlasmaPro 100 Estrelas (Oxford Instruments)

Dry etching processes were carried out on a PlasmaPro 100 Estrelas system (Figure 2.6). The PlasmaPro 100 Cobra from Oxford Instruments allows inductively coupled

plasma (ICP) etching as well as Reactive-Ion Etching (RIE). It is designed to perform dry etching of dielectric, compound semiconductor, metals, or organic materials among others.

Figure 2.6 PlasmaPro 100 Cobra system for dry etching

The PlasmaPro 100 Cobra is compatible with samples up to 4-inch diameter. The system is equipped with a cryogenic module allowing to work down to -120 °C to perform cryoetching. Moreover, it has an interferometer system that allows to full control the etching during the processing.

Several materials can be etched through the different gases lines; Cl<sub>2</sub>, BCl<sub>3</sub>, Ar, SF<sub>6</sub>, C4F<sub>8</sub>, O<sub>2</sub>, CH<sub>4</sub>, CHF<sub>3</sub> and H<sub>2</sub>.

### 1.5.3 RTP As-One 100

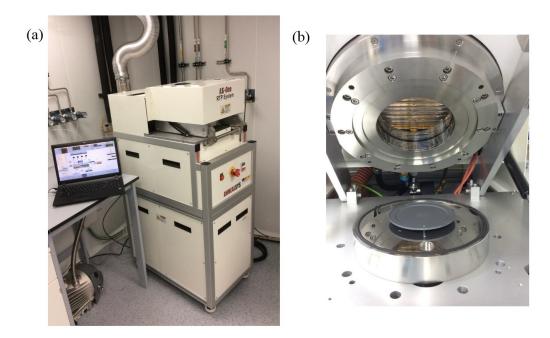

Annealing processes were performed by using the system Rapid Thermal Processing (RTP) As-One 100 (Figure 2.7 (a)). The system is fully recipe controlled and allows working on a temperature range from room temperature up to 1500 °C with an accuracy of  $\pm$  2 °C due to an infrared halogen lamp. System heating ramp rates up to 200°C/s and cooling rates up to -100°C/s are allowed. Nevertheless, the maximum process duration is shorter at high temperature due to the cooling capacity of the machine, i.e. at 950 °C the maximum duration process is limited to 3 hours and at 1500 °C the maximum duration is limited to 30 seconds.

Figure 2.7 Thermal annealing system at the USAL cleanroom

The system is equipped with a chamber designed to process substrates up to 100 mm (4-inch wafers) diameter (Figure 2.7 (b)) and can operate under atmospheric pressure or under vacuum (10<sup>-6</sup> Torr). Small substrates can be introduced using susceptors. The system is equipped with 4 lines of gases (N<sub>2</sub>, O<sub>2</sub>, Ar, He) allowing to modify the environment and flushing the sample during the annealing process.

# 1.5.4 e-beam Evaporator

Metallization of graphene-based devices was performed by using an e-beam evaporator (Figure 2.8 (a)). This e-beam system is designed with two independent chambers and can be isolated or connected using a manual guillotine. The large main chamber is habitually under high-vacuum (10<sup>-9</sup> mbar). Conversely, a small secondary chamber (load-lock) is connected (isolated by the guillotine) to the main chamber working in a pressure range from atmospheric pressure down to 10<sup>-6</sup> mbar. The small volume of the secondary chamber allows to reach 10<sup>-6</sup> mbar pressure in relatively short times (less than 30 minutes) and then load (or unload) the samples into (or from) the main chamber while keeping the main chamber under high-vacuum. The e-beam evaporator has a long distance between the target and the sample (> 0.5 m) and works at very low pressures to ensure a high control on the evaporation rate (less than 1 Å/s) to create high homogeneity thin films on the sample. The evaporation rate, as well as the evaporated metal thickness, is controlled by a quartz crystal. The system is equipped with an e-beam gun from Telemark with a tungsten filament.

**Figure 2.8** Photograph of the e-beam evaporator (a) and gold heated up by the electrons beam (b)

By applying a small emission current to the filament, electrons are accelerated by high voltage (8 kV) and leaded by the magnetic field to the center of the pocket with the desired metal (target). Other low intensity magnetic field known as "XY Sweeping" can be used to move the e-beam diffusing the energy to heat the target material more evenly. Finally, the metal is heated up as the emission current is increased (Figure 2.8 (b)), converting it to a gaseous state and then precipitate it to form a thin film coating the sample.

Several metals can be evaporated in the system using the e-beam evaporator (Au, Ti, Al, Cr, Co, Ni, Pt) as well as some dielectrics (SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>).

# 1.6 Characterization equipment

This section will describe in more detail the equipment used in this PhD for the device characterization. This equipment includes the one used for material characterization and for DC and THz measurements.

## 1.6.1 Profilometer

Profile measurements were performed by using a DektakXT® stylus surface profiler (Figure 2.9). The DektakXT is an advanced thin and thick film step height measurement tool. In addition to profiling surface topography and waviness, the DektakXT system measures roughness in the nanometer range. It has automatic X-Y-theta stages and provides a step-height nanometer resolution.

In addition to taking two-dimensional surface profile measurements, the DektakXT system can produce three-dimensional measurements creating 3D Maps.

Figure 2.9 Photograph of the DektakXT profilometer system

The DektakXT system takes measurements electromechanically by moving a diamond-tipped stylus over the sample surface according to a desired scan length, speed and stylus force. The stylus is linked to a Linear Variable Differential Transformer (LDVT), which produces and processes electrical signals that correspond to surface variations of the sample. After being converted to digital format, these surface variations are stored for display and analysis. The Vision64 application calculates and displays the results of user-selectable analytical functions for measuring surface texture and other parameters to characterize the profile data.

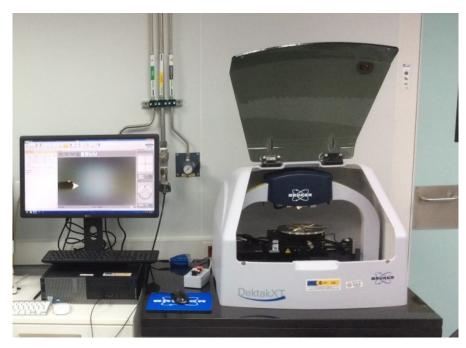

# 1.6.2 Micro Raman Spectrometer (LabRAM HR Evolution)

Raman measurements were performed by using the Micro Raman Spectrometer – LabRAM HR Evolution (Figure 2.10). The LabRAM HR system is suited to both micro

and macro measurements, offering confocal imaging capabilities in 2D and 3D. It is equipped with three different lasers:

- Ventus Solo laser at 532 nm with an output power of 100 mW

- He-Ne laser at 633 nm with an output power of 17 mW

- Diode laser at 770-795 nm with an output power > 200 mW

The LabRAM HR system is suited to both micro and macro measurements since it is equipped with an objective (100x) designed with short free working distance and two objectives (10x and 50x) with long working distance. Measurements performed in this PhD were carried out with the 100x objective distance due to the micro nature of the 2D materials. The 100x objective produces laser spots as small as  $\sim 1~\mu\text{m}^2$  at the focal distance. Incident light can be attenuated till values of 0.01% of the output power. Raman measurements can be performed on the frequency shift range from a relatively low wavenumber cut-off of 50 cm<sup>-1</sup> and with an accurate step below of 2 cm<sup>-1</sup>.

Figure 2.10 Photograph of the Raman spectrometer at USAL facilities

Samples are placed on a XY motorized stage with 0.05  $\mu m$  X-Y step that enables to perform fast confocal Raman imaging measurements. The collection of the scattered light is made with confocal geometry, namely backscattered light is collected by the same objective that focuses the exciting laser beam. Two different diffraction gratings can be used with 1800 grooves/mm or 600 grooves/mm. Raman spectrums are collected by using a 256x1.024 pixels Synapse CCD detector (with a spectral range of 200-1.050 nm) that is cooled by Peltier effect.

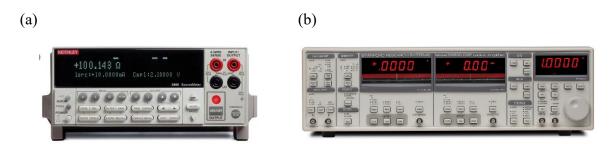

## 1.6.3 Lock-in Amplifier & Keitley 2410

The experimental data about electrical characterization presented in this Thesis were acquired using either lock-in amplifiers or Keithley sourcemeters, which are capable of measuring small signals adding extremely low noise levels. DC measurements were performed by using double channel Keithley 2412 sourcemeter units (SMU) (Figure 2.11 (a)). This SMU provides precision voltage and current sourcing as well as measurement capabilities.

Lock-in amplifiers where employed for AC/DC measurements in THz detection experiments. The lock-in amplifiers employed are the model Stanford Research SR830 as the one showed in Figure 2.11 (b). An alternate AC signal is collected by the input channels (current or voltage can be used) and filtered by the amplifier. The filtering works in such a way that the only component which is selected by the instrument has the same frequency than a reference signal to which is phase-locked (i.e. has a phase relation which is fixed in time). This reference signal can be external (i.e. the signal frequency of the mechanical chopper) or generated by the lock-in amplifier itself. This method is known as phase-sensitive detection (PSD). All the other components of the input signal are filtered out, resulting in efficient noise rejection and high accuracy.

Figure 2.11 Photograph of the Lock-in SR830 (a) and Keithley 2412 (b)

The PSD relies on simple trigonometry, as explained in the following. Considering that an input signal ( $V_{sig}$ ) can be writen as  $V_{sig} \sim \sin(\omega_r t + \theta_{sig})$  and the sinusoidal reference signal ( $V_L$ ) as  $V_L \sim \sin(\omega_L t + \theta_{ref})$ . The two signals are multiplied by the lockin; the resulting signal is as follows:

$$\frac{1}{2}V_{sig}V_{L}\cos((\omega_{r}-\omega_{L})t+\theta_{sig}-\theta_{ref})-\frac{1}{2}V_{sig}V_{L}\cos((\omega_{r}+\omega_{L})t+\theta_{sig}+\theta_{ref})$$

(2.1)

The output signal described by Equation 2.1 consists of two sinusoidal signals, one at the frequency that is the difference of the two input frequencies  $(\omega_r - \omega_L)$ , and one at the sum of these frequencies  $(\omega_r + \omega_L)$ . When the input signal has the same frequency than the reference signal (i.e.  $\omega_r = \omega_L$ ), the difference signal becomes a DC value. When the PSD output is passed through a low pass filter, the component  $(\omega_r + \omega_L)$  is filtered out and the resulting signal is as follows:

$$\frac{1}{2}V_{sig}V_L\cos(\theta_{sig}-\theta_{ref})$$

(2.2)

Equation 2.2 shows that the intensity of the resulting DC signal is proportional to the input signal's one ( $V_{sig}$ ). All the components at frequencies other than the one of the reference are filtered out. By adjusting  $\theta_{ref}$  on the lock-in amplifier we can make  $\theta_{sig} = \theta_{ref}$  and the difference will be equal to zero; in this case the resulting signal is directly proportional to  $V_{sig}$  and can be measured. Conversely, if the difference between  $\theta_{sig}$  and  $\theta_{ref}$  is equal to  $\pi/2$ , the output signal will be equal to zero.

Chapter 3

Silicon FETs

# 2.1 Introducción

Semiconductor plasmonic FETs operating as detectors in the THz range has been demonstrated [26]. FETs fabricated on III-V compounds [27],[28] or silicon [29] are the two principal researching lines in solid-state plasmonic THz detectors. Nevertheless, one of the major advantages of employing Silicon FETs lies in the capability to produce low cost, scalable and reliable commercial THz technology. Moreover, to facilitate this task, the development of THz devices can be complemented with accurate simulations. This can be performed by using different tools such us the Technology Computer-Aided Design (TCAD) Synopsys simulator [30] to obtain the performance of the device for both DC and AC simulations. This chapter addresses the study of two different silicon-based devices as THz detectors. The first one lies with the theoretical and experimental studies of strained-Si MODFETs. An analysis employing Synopsys TCAD was performed. The second one is the use of silicon FINFET devices.

# 2.2 Si/SiGe technology

Throughout this section we will present some basic concepts about the Silicon (Si), Germanium (Ge) and Si/SiGe systems necessary to understand the behavior of the transistors showed in this chapter. As these transistors rely upon the strain of a pure-Si layer sandwiched between relaxed layers or SiGe a right understanding of the properties of the. Si/SiGe material system is necessary

Accordingly, the most basic properties (mobility, GAP, band structures, ...) of the two simple semiconductors (Si and Ge) will be presented. Also, the properties of Ge/SiGe and Si/SiGe heterojuncions will be revised. A particular emphasis will be placed on the influence of strain on the heterojunctions (valence and conduction bands offset, mobility, ...).

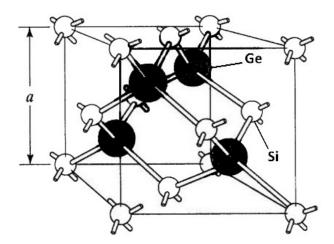

## 2.2.1 Si, Ge and SiGe systems

The crystal structure of silicon and germanium is classified under the diamond structure, and thus it has two atoms in a primitive cell: The crystal lattice can be represented as two interpenetrating face centered cubic lattices (FCC) with a cube side of 0.543 nm in the case of Si and 0.566 nm in the case of Ge (Figure 3.1). The structure is visualized as a tetrahedron with four vertices of the first FCC lattice at (0,0,0), (a/2,0,0), (0,a/2,0) and (0,0,a/2) and an additional atom added to the center of this tetrahedron. The additional lattice is displaced diagonally by 1/4 with respect to the first FCC lattice.

Figure 3.1 The unit cell and diamond lattice structure for Si, SiGe, and Ge [31]

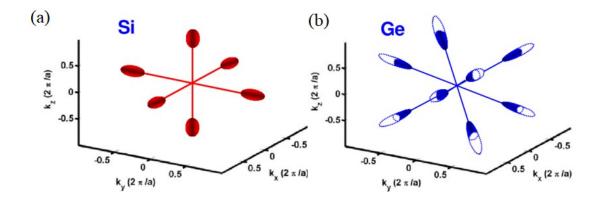

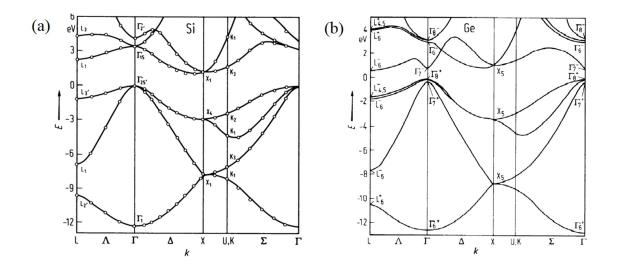

In silicon, the conduction band minima (Figure 3.2 (a)) lie on the six equivalent  $\Delta$ -lines along the <100>-directions and occur at about 0.85% of the way to the Brillouin zone boundary (Figure 3.3 (a)), i.e. near the X points of the first Brillouin zone, the minima are called X- valleys. In bulk Ge the eight equivalent minima lie in the L points, i.e. in the limit of the Brilloin cell (Figure 3.3 (b)).

**Figure 3.2** Si (a) and Ge (b) equi-energy valleys. [32]

The material system  $Si_{1-x}Ge_x/Si_{1-y}Ge_y$  is used to fabricate high-speed transistors based in the heterojunction between both materials alloys. The flexibility of the material system allows the design of FETs and HBTs (Heterojunction Bipolar Transistors) by controlling the values of the molar fraction at each side of the heterojunction, the vertical doping profile and the epitaxial growth as one of the layers must be under strain. We will limit ourselves to describe the specific system used in the transistors that this work deals with.

Figure 3.3 Band structure of Si (a) and Ge (b) [33]

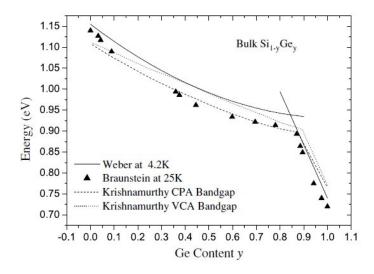

The study of bulk (unstrained)  $Si_{1-x}Ge_x$  shows that as the molar fraction of Ge is increased, the values of the bandgap and the energy band structure are modified, this has a large impact, for instance, on carrier mobility. As above stated, since we are dealing with n-channel devices we will restrict the scope of this Thesis to the analysis and discussions of electrons in the conduction band.  $Si_{1-x}Ge_x$  alloy with Ge molar fractions below 0.85 has a band conduction essentially equal to the one of bulk Si, accordingly the electron masses are essentially the same than in Si and the only noticeable change for electrons is the value of the bandgap. The dependence of this latter with the molar faction approximately follows the Vegard's rule:

$$E_{GAP} = 1.12 - 0.41x \, eV \quad (x < 0.85)$$

(3.1)

$$E_{GAP} = 1.86 - 1.2x \, eV \quad (x > 0.85)$$

(3.2)

For Ge molar fractions larger than 0.85 the SiGe the conduction band is alike the one of germanium. Both equations are experimentally verified (see Figure 3.4):

Figure 3.4 Energy GAP on Bulk Si<sub>1-x</sub>Ge<sub>x</sub> at low temperature [34]

Figure 3.4 shows the dependence of the energy bandgap with the molar fraction of Ge in a  $Si_{1-x}Ge_x$  alloy. The weak dependence of the bandgap on temperature for a given value of the molar fraction follows the empirical rule:

$$E_G(T) = E_G(0) - \frac{\alpha T^2}{T + \beta}$$

(3.3)

the parameters are given in Table 3.1:

|               | Germanium             | Silicon               |

|---------------|-----------------------|-----------------------|

| $E_G(0)$ (eV) | 0.7347                | 1.166                 |

| α (eV/K)      | 4.77·10 <sup>-4</sup> | 4.73·10 <sup>-4</sup> |

| β (K)         | 235                   | 636                   |

**Table 3.1** Constant parameters for the Energy GAP of Ge and Si

Since SiGe technology bears a great interest for cryogenic and aerospace applications the bandgap dependence on temperature is of interest [35]. Nevertheless, in this Thesis we focus on studies at room temperature.

## 2.2.2 Strain on SiGe composite

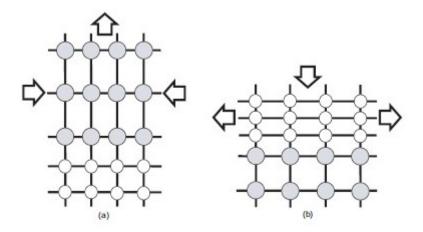

Epitaxial growth of  $Si_{1-x}Ge_x$  layers can be performed over Si or Ge substrates allowing to obtain almost any composition in the range of 0 < x < 1. Since the grown layer has a different lattice constant than the substrate, the upper layer will undergo a

mechanical strain. A higher lattice constant of the grown layer than the one of the substrate will lead to a compressive strain of the crystal unit cell in the normal plane (Figure 3.5 (a)). Conversely, a lower lattice constant of the grown layer will produce a tensile strain in that plane (Figure 3.5 (b)).

Figure 3.5 Compressive (a) and tensile (b) strain

When the growth is not performed appropriately, the strain can be total or partially relaxed creating dislocations, changes in the symmetry plane, etc. that are highly harmful for the charge transport, downgrading the performance of the devices fabricated with such heterostructures. A high-quality strained layer is achieved by an elastic deformation of the unit cell during the growth of the epitaxial layer (this is indicated in Figure 3.5 by the vertical arrows).

The strain parameter  $(\bar{\varepsilon})$  is defined as:

$$\frac{-}{\varepsilon} = \frac{a_{substrate} - a_{layer}}{a_{substrate}}$$

(3.4)

Where,  $a_{substrate}$  is the lattice constant of the substrate, and  $a_{layer}$  is the lattice constant of the layer grown on the substrate. The strain parameter provides information about the magnitude of the mismatch between the epitaxial layer and the substrate. Also, its sign indicates if the strain is compressive (negative strain) or tensile (positive strain). For Si<sub>1-x</sub>Ge<sub>x</sub> alloys, the lattice constant of the compound will increase with the value of the molar fraction as given by the Vegard's law [36]. There are two components of the strain:

- *Hydrostatic strain*, also called volumetric strain or dilatation, is a strain that is equal in all normal directions, with no shear components. It is a change in the volume of a body (in our case this is represente by the unit cell), but not in its shape (Figure 3.6 (a)).

- *Uniaxial* (or biaxial) strain occurs when only one (or two) component of the principal strains is nonzero, changing both the volume of a body and its shape (Figure 3.6 (b)).

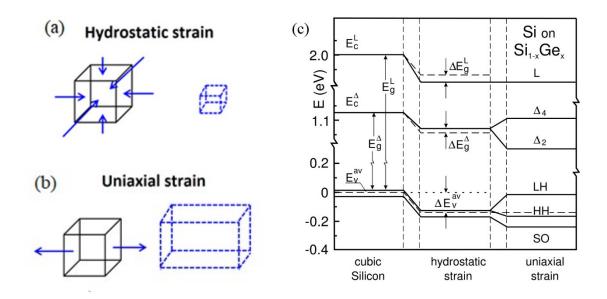

**Figure 3.6** Hydrostatic (a) and Uniaxial strain (b). Contribution of the hydrostatic and uniaxial strain on Si growth on  $Si_{1-x}Ge_x$  (c)

The hydrostatic strain component leads to an overall downward shift of the average valence band level  $E_{\nu}^{av}$  by  $\Delta E_{\nu}^{av}$ , but also modifies the  $\Delta$  and L bandgaps by, respectively, the amounts of  $\Delta E_{g}^{\Delta}$  and  $\Delta E_{g}^{L}$ , respectively (Figure 3.6 (c)). The energy would be determined by the strain parameter. For Si grown on bulk Si<sub>1-x</sub>Ge<sub>x</sub>, since the lattice constant of Si is lower than the one of the SiGe substrate the epitaxial Si layer is under biaxial tensile strain. In this configuration, the degenerated  $\Delta_{6}$  valleys of the Si layer are split into four equivalent valleys ( $\Delta_{4}$ ) which are shifted up in energy, and two equivalent valleys ( $\Delta_{2}$ ) which are shifted down in energy (Figure 3.7 (a)). In unstrained Si and Ge, the heavy-hole (HH) and light-hole (LH) bands are degenerated at the  $\Gamma$  point. Biaxial strain splits the degeneracy by shifting the HH band below the LH band though the designation of "light" and "heavy" loses its meaning, since the hole effective masses become highly anisotropic with strain [37].

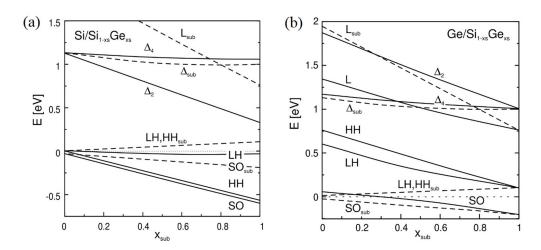

**Figure 3.7** Conduction and Valence energy shifts for Si/Si<sub>1-x</sub>Ge<sub>x</sub> (a) and Ge/Si<sub>1-x</sub>Ge<sub>x</sub> (b) [38].

An opposite behavior is found in the case of a biaxial compressive strain (i.e. Ge on  $Si_{1-x}Ge_x$ ) where the  $\Delta_4$  valleys are shifted down in energy, while the  $\Delta_2$  valleys are shifted up. In the case of the valence band, the HH band moves above the LH band (Figure 3.7 (b)).

Since in strained materials both valence and conduction bands are shifted in energy the bandgap is modified. Figure 3.8 shows the variation of the bandgap of strained-Si and strained-Ge<sub>x</sub>Si<sub>1-x</sub> layers versus the Ge molar fraction.

Figure 3.8 Energy Gap shift of Si/Ge composites [39]

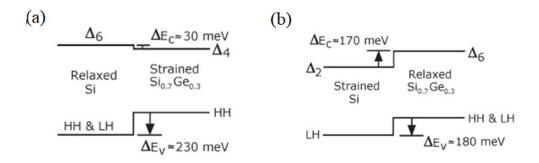

A thin layer of Si<sub>1-x</sub>Ge<sub>x</sub> grown on a substrate with lower lattice constant (i.e. Si), produces a biaxial compressive strain on the upper layer. Figure 3.9 (a) shows the offsets produced on the conduction and valence bands when a strained thin Si<sub>0.7</sub>Ge<sub>0.3</sub> layer is grown on a relaxed Si substrate. A small offset of 30 mV is produced on the conduction band while a significant energy discontinuity (an offset of 230mV) results in the valence band. This type of heterostructures is useful to build p-FETs as holes can be confined.

Figure 3.9 Compressive (a) and tensile (b) strain

In a similar way, a thin layer of Si can be grown under tensile biaxial strain on a relaxed SiGe (usually called virtual substrate as SiGe wafers do not exist). Figure 3.9 (b) shows the offset generated on the conduction and valence bands of a heterojunction formed bu growing a strained-Si layer on a relaxed Si<sub>0.7</sub>Ge<sub>0.3</sub> virtual substrate. Unlike the compressive strain case, under tensile strain large offsets are obtained for both conduction (170 mV) and valence (180 mV) bands allowing the confinement electrons and holes. Thus, these types of junctions are useful to build p- and n- FETs. A pure strained-Si channel will allow excellent electron mobility as compared to SiGe channels since no alloy carrier scattering will be present. As above pointed out no real substrates of Si<sub>1-x</sub>Ge<sub>x</sub> exist. Therefore, strained-Si/Si<sub>1-x</sub>Ge<sub>x</sub> junctions are fabricated as follows: a conventional silicon wafer is used as the starting substrate and then a thick Si<sub>1-x</sub>Ge<sub>x</sub> layer is grown gradually increasing the Ge molar fraction from zero till the desired final molar fraction. Then a relatively thick layer of relaxed Si<sub>1-x</sub>Ge<sub>x</sub> with a uniform Ge molar fraction is grown on the graded SiGe layer to act, as a relaxed virtual substrate (usually knows as the set back layer). Finally, the strained Si layer is grown on this virtual substrate.

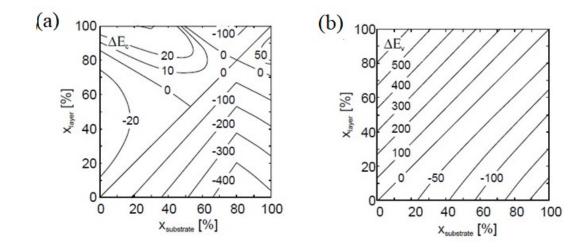

**Figure 2.10** Conduction and Valence offsets as function of the molar fraction on the substrate [38]

Figure 3.10 shows the distribution of the theoretical offsets of both conduction (a) and valence (b) bands for strained Si<sub>1-xlayer</sub>Ge<sub>1-xlayer</sub> grown on Si<sub>1-xsubstrate</sub>Ge<sub>xsubstrate</sub>. There are considerable disagreements between theoretical and measured valence band-offset values in literature [38], [40], [41].

## 2.2.3 Strain and mobility

There are important parameters such as doping density profiles, type of carriers, interface quality, oxide trap density, semiconductor bulk defect density among other that assess the material quality. Nevertheless, the most important transport parameter in a semiconductor is carrier mobility [42]. Carrier mobility can be obtained using a simple model which gives the approximate relation between scattering time (average time between scattering events) and mobility by the next equation:

$$\mu = q \frac{\tau}{m^*} \tag{3.5}$$

where q is the absolute value of the elementary charge,  $m^*$  is the carrier effective mass, and  $\tau$  is the average scattering time. Since mobility has been always a key parameter to properly desing high-performance semiconductor devices, there is a huge interest in the development of theoretical models to describe the dependence of carrier mobility on electric field, temperature, doping concentration, etc. An accurate estimation of the theoretical maximum values of mobility (of holes and electrons) can be obtained in bulk materials like Si, Ge and then estimate the expected mobility values in strained-Si/SiGe heterostructures [43].

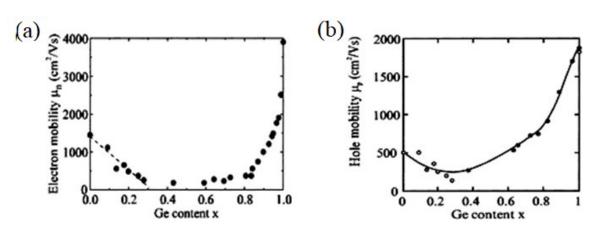

Figure 3.11 Si<sub>1-x</sub>Ge<sub>x</sub> Electron (a) and hole (b) Hall mobility vs composition at 300 K [43]

Figure 3.11 shows the electron (a) and hole (b) Hall mobility as a function of the Ge molar fraction in relaxed  $Si_{1-x}Ge_x$ . Electron mobility decreases abruptly from the pure materials (Si or Ge) and drops by two orders of magnitude for Ge molar fractions in the range of 0.3 < x < 0.8. A similar behavior is found in hole mobility

As described above, biaxial strain results in changes on the conduction and valence bands of Si that directly affect carrier mass, effective density of states and, eventually, intra- and inter- valley scattering.

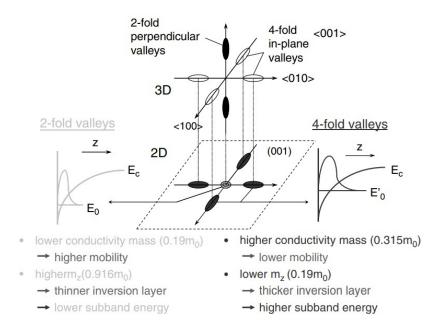

**Figure 3.12** Schematic diagram of characteristics of the two- and four-fold valleys in two-dimensional electrons on a (100) surface [44], [45].

In a thin strained-Si layer, electrons essentially exhibit the same anisotropy in their effective mass than in bulk Si [46]. It is composed of two light transversal effective

masses,  $m_t = 0.19 \, m_0$ , where  $m_0$  is the electron mass in free space, and a heavy longitudinal effective mass,  $m_l(=0.916 \, m_0)$ . As a result, the twofold degenerate valleys have the effective masses of  $m_t$  in parallel and  $m_l$  in perpendicular to the heterojunction interface, while the fourfold degenerate valleys have  $m_t$  and  $m_l$  effective masses in parallel and  $m_t$  in perpendicular to the heterojunction interface. These differences in the effective mass leads to a variety of differences in physical properties between the twofold and the fourfold valleys. For instance, the conductivity mass parallel to the heterojunction interface is lower in the twofold valleys than in the fourfold valleys and, thus, the mobility of electrons in the twofold valleys is higher than the one in the fourfold valleys.

An epitaxial thin layer of Si on unstrained Si<sub>1-x</sub>Ge<sub>x</sub>, as Si has a shorter lattice constant than the one of SiGe, Si is under biaxial tensile strain. Accordingly, the strain splits the six equivalent valleys at the minima of the conduction band into twofold perpendicular and fourfold in plane valleys leading to an increase of the mobility through two mechanisms. The first one is the increase of the occupancy of the twofold valleys leading to a lower conductivity mass than in bulk Si and, then, to an improvement of the electron mobility (Figure 3.13). The second one is the suppression of inter-valley scattering between the twofold and the fourfold valleys [45] when carriers are drifted by low and moderate longitudinal electric fields in a FET.. Conversely, biaxial compressive strain leads to a decrease in electron mobility. because the lower energy of the four-fold valleys and thus a higher occupancy of the electrons in valleys having high conductivity mass.

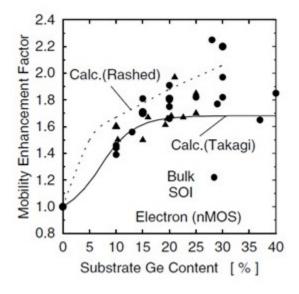

Figure 3.13 Mobility enhancement factor vs Ge molar fraction on strained-Si [45].

The relationship between electron mobility in n-channel Si/SiGe devices has been systematically investigated by using strained-Si FETs fabricated on relaxed SiGe substrates. Figure 3.13 shows experimental results for the mobility enhancement factor [45], defined as the ratio of the mobility in strained-Si MOSFETs and that in conventional (unstrained) Si FETs, as a function of the Ge content of the substrate. Theoretical results forecasting a mobility enhancement factor are also shown [47].

Agreement between the experimental and theoretical results is fairly good. An enhancement factor of roughly two is obtained.

# 2.3 Strained-Si MODFETs

### 2.3.1 Introduction

A modulation-doped FET (MODFET) or High-electron mobility FET (HEMT) is a field-effect transistor consisting of a junction between two different materials with different band gaps, creating a heterojunction with a non-doped layer called the channel. Electrons (or holes) are supplied by a high doped layer, usually degenerated and relatively thin called supply-layer, close to a heterojunction, and transferred to the channel. This electron (or hole) transfer is allowed since the discontinuities created as consequence of the different energy on the conduction ( $\Delta$ Ec) and valence bands ( $\Delta$ Ev).

MODFETs present several advantages; they have high gain, so they are useful as amplifiers; a high switching speeds can be achieved since the main charge carriers in MODFETs are majority carriers, and minority carriers are not significantly involved as consequence of the different energy bands; and extremely low noise values because the current variation in these devices is low compared to other FETs.

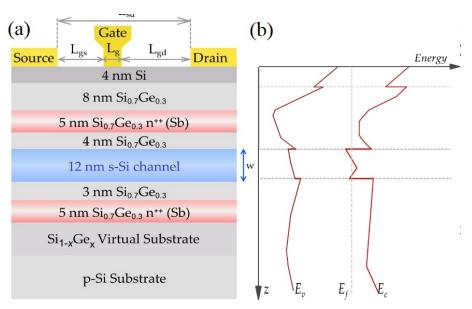

There are several material combinations to design a MODFET. One of them is based on the SiGe technology. Three different Si/SiGe based MODFETs can be designed. N-channel- or n-MODFETs are based on strained-Si channels [48], [49] and the channel on p-MODFETs are based on SiGe or Ge, with, usually, a molar fraction of 30% [50], [51]. This chapter focuses on n-channel strained-Si MODFETs with two different highly doped supply layers near to the nominally undoped silicon channel.

# 2.3.2 Device description

N-channel devices under study in this work are based on the Si/SiGe system. Their layout is given in Figure 3.14 (a). The epistructure of the MODFETs is as follows: first, a thick (3□m) relaxed linearly graded SiGe virtual substrate was grown over a p-doped conventional Si wafer. The final top Ge molar fraction in the virtual substrate was 0.3. The structure has an undoped 12 nm tensile strained Si channel sandwiched between two n-doped Si<sub>0.70</sub>Ge<sub>0.30</sub> relaxed supply layers (reddish layers) to generate a high density of electrons in the strained-Si quantum well [52], [53]. The highlighted bluish layer marks out the strained-Si quantum well. Pt/Au were evaporated on a very thin silicon layer to fabricate the Schottky-gate. The gate was not symmetrically placed between source and drain. A more detailed description of the transistor fabrication can be found in [52]. Our strained-Si MODFETs used in this work were fabricated by Thomas Hackbarth (Daimler) and supplied to us by Dr. Kristel Fobelets (Imperial College London).

**Figure 3.14** (a) Epistructure of the Si/SiGe MODFETs showing the vertical layout of the transistors. (b) Conduction and Valence band profiles and the Fermi level under the gate in equilibrium.

As we showed above, the material system Si/SiGe allows the creation of a biaxial tensile straind layer of silicon on a relaxed SiGe virtual substrate that may be capitalized to fabricate strained—Si n-channel FETs with a theoretical enhancement of the channel electron mobility by a factor nearly two when using values of the Ge molar fraction in the substrate in excess of 0.3 [54], [55]. High-electron mobility FETs (HEMTs), also known as Heterostructure FETs (HFETs) or Modulation-Doped FETs (MODFETs), have been recognized as one of the more suitable candidates to develop soild-state sources and detectors of sub-THz and THz detectors [19]. Si/SiGe HEMTs exhibit competitive advantages as compared to other FETs technologies: Si MOSFETs lack of a high-mobility channel and III-V HEMTs lack of substrate compatibility with Si wafers and, additionally, it is well known that they commonly lead to extensive reliability concerns.

From the above it follows that tensile strained silicon channels will allow us to build high-mobility FETs that will be excellent candidates to detect and generate THz radiation. A vertical cut of the energy band diagram of an unbiased typical Schottky-gate strained-Si/SiGe is given in Figure 3.14 (b). The value of the conduction band offset of the heterojunction Si/Si<sub>0.70</sub>Ge<sub>0.30</sub> is about 180 meV according to literature [56] that would ensure an excellent electron confinement in the strained-Si quantum well, necessary for room temperature high-mobility operation of the transistor. The results presented in this work are based on this epilayer. Table 3.2 summarizes the geometrical parameters of the strained-Si MODFETs that were studied.

|               | $L_{DS}$ ( $\mu$ m) | L <sub>GS</sub> (µm) | $L_{G}(nm)$ | $W_G(\mu m)$ |

|---------------|---------------------|----------------------|-------------|--------------|

| Device 1 (D1) | 2                   | 1                    | 100         | 30           |

| Device 2 (D2) | 2                   | 1                    | 250         | 30           |

| Device 3 (D3) | 2                   | 1                    | 500         | 30           |

**Table 3.2** Geometrical and electrical parameters of the strained-Si MODFETs under study.

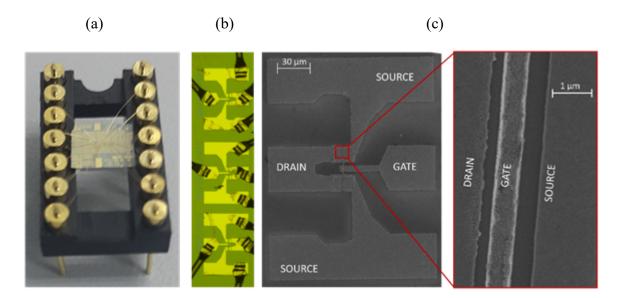

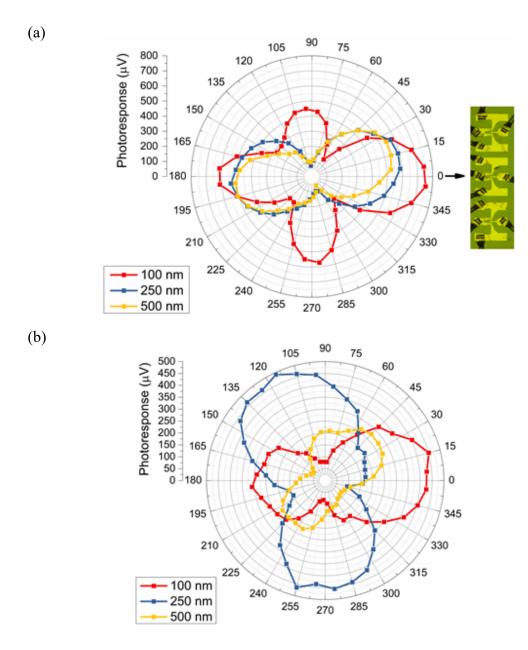

**Figure 3.15** Strained-Si MODFETs under study mounted and bounded on a DIP14 (a) and their optical microscope image (b). (c) SEM image of Device 3 (500 nm T-gate transistor).

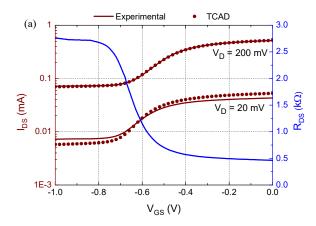

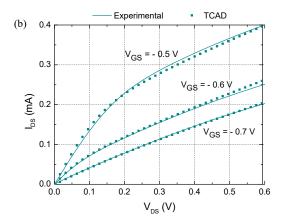

The channel's length ( $L_{DS}$ ) and width ( $W_G$ ) were kept constant for all devices ( $L_{DS}$ =2  $\mu$ m,  $W_G$ = 30  $\mu$ m). However, the gate lengths of the transistors were varied. Transistors with 100-, 250- and 500-nm gate length were characterized. The gates were asymmetrically placed between the source (S) and the drain (D) contacts in all transistors; the distance between the right edge of the source and the left edge of the gate ( $L_{GS}$ ) was equal to 1 $\mu$ m for all the transistors (Table 3.2). An asymmetrical position of the gate is of interest to enhance THz detection by a transistor [57]. Measuring devices with different values of the gate length allows the study of the influence of the gate length on the performance of the transistors as THz detectors and on the coupling of the incoming THz radiation to the device channel. Strained-Si MODFETs with different gate lengths were mounted and wire-bonded on the same dual in-line package (DIP14) showed in (Figure 3.15 (a)). An optical microscope image of the three different devices under study is given in Figure 3.15 (b). A SEM image of D3 with  $L_G$ =500 nm is shown in Figure 3.15 (c).

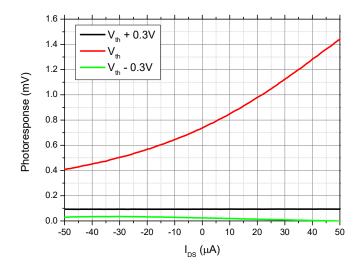

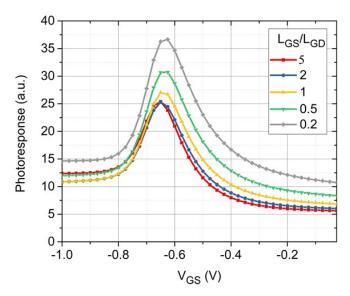

## 2.3.3 TCAD modelling

Dyakonov and Shur obtained an analytical solution of the unidimensional Euler equation that demonstrated the ability of plasma-waves developed in FET channels to generate and detect THz radiation [18], [19]. Nevertheless, a single equation cannot account for all the technologically relevant parameters (such as doping profiles, high electric fields that locally modify the carrier mobility, device geometry, etc.) that condition the performance of a FET as a THz detector. Thus, a deeper study is necessary for that purpose. This work presents a theoretical study based on Technology Computer-Aided Design (TCAD) simulations to investigate the transistor response to THz radiation excitation. Two-dimensional (2D) TCAD simulations were validated through comparison with both DC and THz measurements.

## 2.3.3.1 Basic equations

This section summarizes the most important physical models used in the simulations of the strained- Si MODFETs. An, insufficient, first description of the charge transport in a transistor may be achieved through the numerical solution of the drift-diffusion model (DDM) coupled to a Poisson equation solver (Equation (3.6)) and the continuity equations for electrons (Eq. (3.7)) and holes (Eq. (3.8)) [58]:

$$\nabla^2 \varphi = -\frac{q}{\varepsilon} \left( p - n + N_D^+ - N_A^- \right) \tag{3.6}$$

$$\frac{\partial n}{\partial t} = \frac{1}{q} \left( \overrightarrow{\nabla} \cdot \overrightarrow{J}_n \right) - U_n \tag{3.7}$$

$$\frac{\partial p}{\partial t} = -\frac{1}{q} \left( \overrightarrow{\nabla} \cdot \overrightarrow{J}_p \right) - U_p \tag{3.8}$$

where  $\varphi$  is the electric potential, q is the absolute value of the electron charge, n/p is the electron/hole concentration,  $N_D^+$  ( $N_A^+$ ) is the ionized donor (acceptor) concentration,  $\varepsilon$  is the local material permittivity and  $U_n^-$  ( $U_p^-$ ) represents the net electron (hole) recombination rate.  $\vec{J}_n^-$  ( $\vec{J}_p^-$ ) is the current density of electrons (holes) in the drift-diffusion model given by the equations (3.9) and (3.10):

$$\overrightarrow{J_n} = q\mu_n(u_n)[\overrightarrow{nE} + \overrightarrow{\nabla}(u_n n)]$$

(3.9)

$$\overrightarrow{J_p} = q \mu_p(u_p) [n\overrightarrow{E} + \overrightarrow{\nabla}(u_p p)]$$

(3.10)

where  $\vec{E}$  is electric field,  $\mu_n$   $\mu_n$  ( $\mu_p$ ) is the electron (hole) mobility and  $\mu_n$  ( $\mu_p$ ) is the electron (hole) thermal voltage. In deep-submicron FETs, the drain and gate biases give rise to large electric fields that rapidly change over small length scales giving origin to nonlocal phenomena that will dominate the transistor performance [52], [53]. As carriers are intensely heated by the electric field in the channel of deep-submicrometer FETs energy balance equations accounting for electron and hole heating and energy relaxation in the device must be self-consistently added to the transport model. Since, the DDM only considers moment relaxation [47], it is unable to describe hot carrier transport. As channel mobility is closely dependent on the carrier temperature an extended model needs to be used to study the electric properties of deep-submicron FET transistors used in plasma wave THz detection. This extended model is known as the hydrodynamic model (HDM).

The HDM [47], [59] includes carrier energy balance by coupling to the set of DDM equations (Eqs. (3.6) - (3.8)) and the electron and hole energy flow densities (Eqs. (2.9) - (2.10)) that are given as:

$$\vec{\nabla} \cdot \vec{S_n} = \frac{1}{q} \vec{J_n} \cdot \vec{E} - \frac{3}{2} \left( p \frac{u_n - u_0}{\tau_n} + \frac{\partial (u_n n)}{\partial t} \right)$$

(3.11)

$$\vec{\nabla} \cdot \vec{S_p} = \frac{1}{q} \vec{J_p} \cdot \vec{E} - \frac{3}{2} \left( p \frac{u_p - u_0}{\tau_p} + \frac{\partial (u_p p)}{\partial t} \right)$$

(3.12)

where  $\overrightarrow{S_n}$   $(\overrightarrow{S_p})$  is the electron (hole) energy relaxation time,  $u_n$   $(u_p)$  is the above-referred electron (hole) thermal voltage and the electric field that is self-consistently obtained from the Poisson equation.

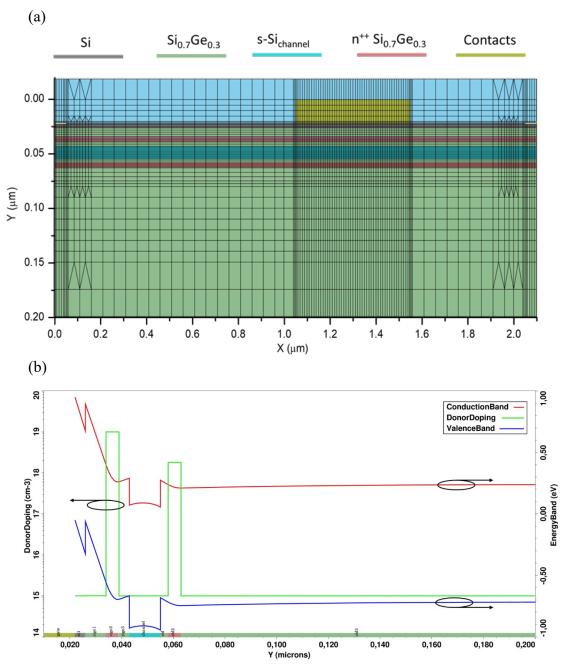

Strained-Si MODFET is essentially a majority carrier device, then the hole energy balance equation (Eq. 3.12) was disregarded in our model. In the present work, a two-dimensional HDM for electron transport and DDM for hole transport (Eqs. (3.6) -(3.11)) was used in TCAD simulations. Carrier relaxation times were obtained from uniform-field Monte Carlo simulations [60], [61]. In TCAD simulations impurity de-ionization, Fermi-Dirac statistics and mobility degradation due to both longitudinal and transverse electric field were considered. All TCAD simulations were carried out at room temperature.

## 2.3.3.2 Mobility models

As we mentioned above, carrier mobility is a key parameter in the semiconductor technology, thus, accurate models are necessary to describe carrier mobility,  $\mu_n$  and  $\mu_p$ , in the device. We selected two different models [30]; the first one is a general mobility model for electrons and holes based on the concentration and the second one is a mobility model based on the surface scattering conditioning the mobility in device.

#### 2.3.3.2.1 Concentration model

For simple materials as Si, a concentration- and temperature-dependent empirical mobility model is given by the equations (3.13) and (3.14):

$$\mu_{0n} = MUN.MIN + \frac{MUN.MAX \left(\frac{T}{300}\right)^{NUN} - MUN.MIN}{1 + \left(\frac{T}{300}\right)^{XIN} \left(\left(\frac{N_{total}}{NREFN}\right)^{ALPHAN} + \left(\frac{N_{total}}{NREFN2}\right)^{3}\right)}$$

$$ddddd$$

(3.13)

$$\mu_{0p} = MUP.MIN + \frac{MUP.MAX \left(\frac{T}{300}\right)^{NUN} - MUP.MIN}{1 + \left(\frac{T}{300}\right)^{XIP} \left(\left(\frac{N_{total}}{NREFP}\right)^{ALPHAP} + \left(\frac{N_{total}}{NREFP2}\right)^{3}\right)}$$

(3.14)

where  $N_{total}$  is the local total impurity concentration (in cm<sup>-3</sup>) and T is temperature (in K). The default values used for silicon are given in Table 3.3:

| Parameter | Silicon  | Parameter | Silicon  |

|-----------|----------|-----------|----------|

| MUN.MIN   | 55.24    | MUP.MIN   | 49.70    |

| MUN.MAX   | 1429.23  | MUP.MAX   | 479.37   |

| NrefN     | 1.072E17 | NrefP     | 1.606E17 |

| NrefN2    | 1E30     | NrefP2    | 1E30     |

| Nun       | -2.3     | Nup       | -2.2     |

| XIN       | -3.8     | XIP       | -3.7     |

| ALPHAN    | 0.73     | ALPHAP    | 0.7      |

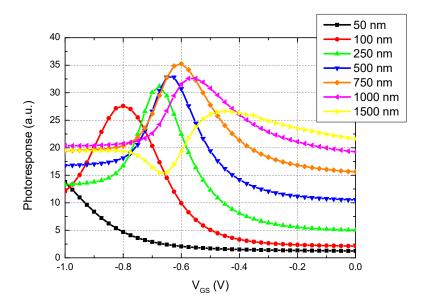

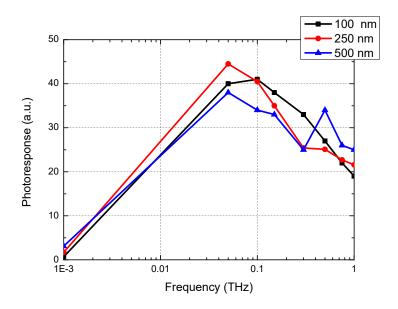

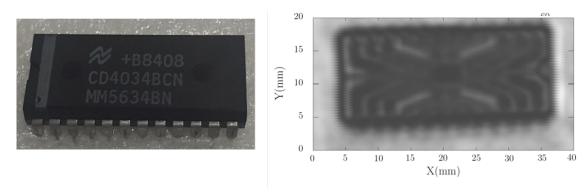

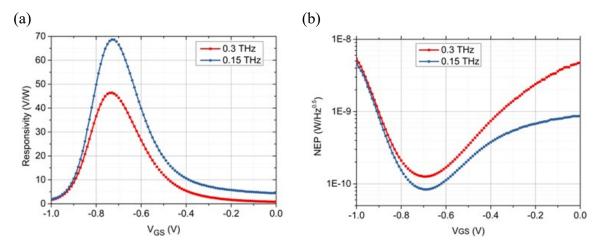

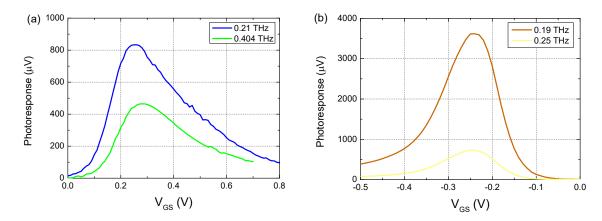

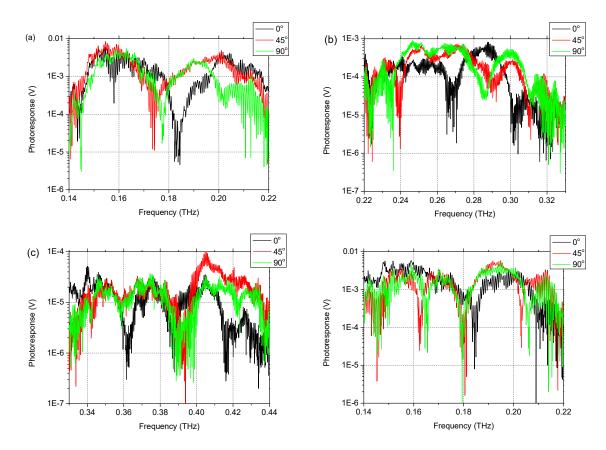

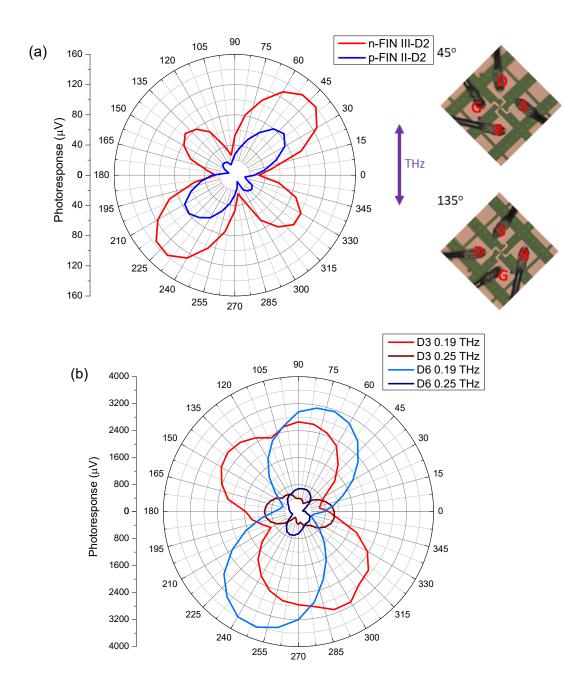

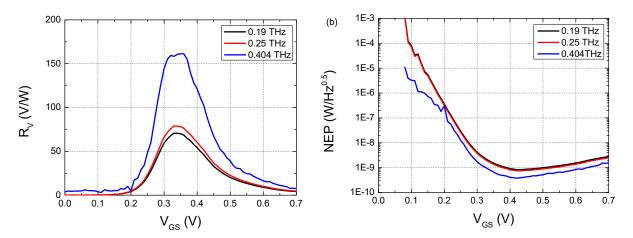

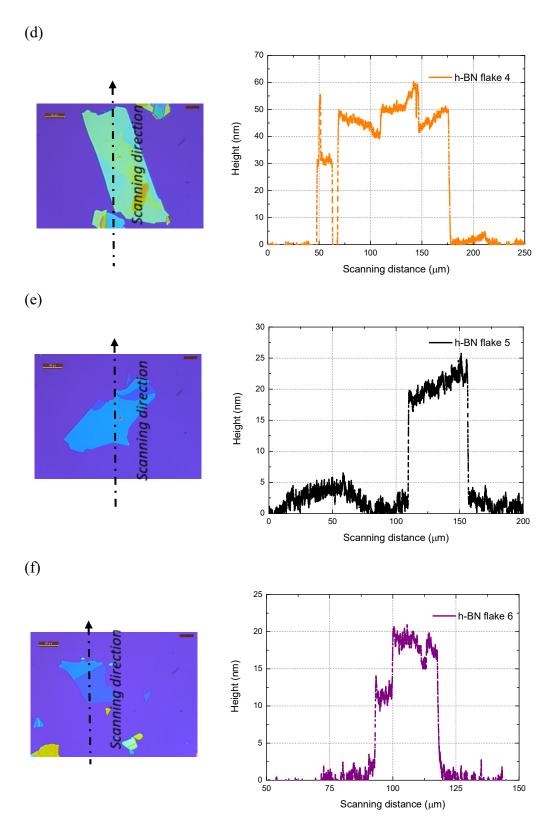

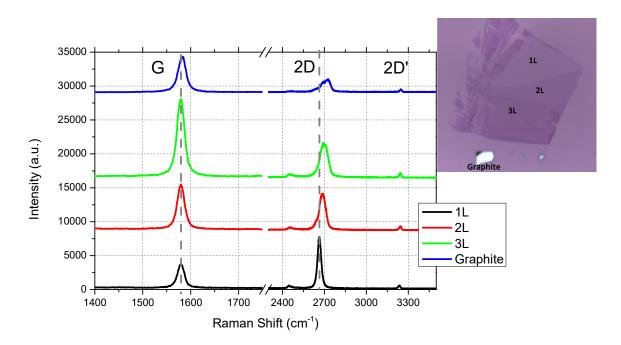

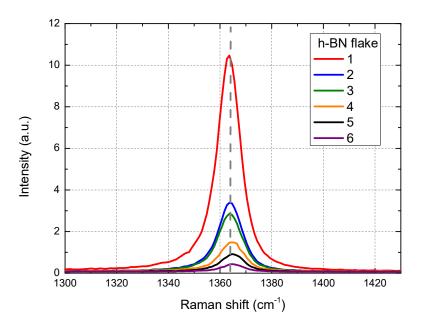

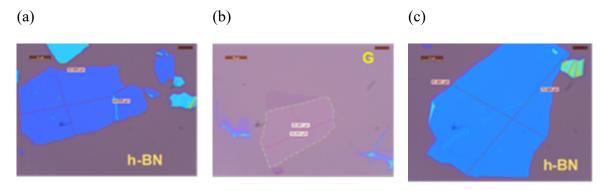

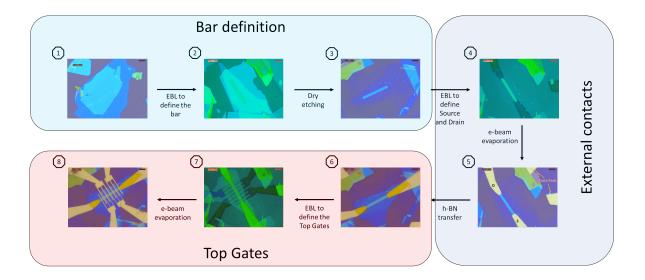

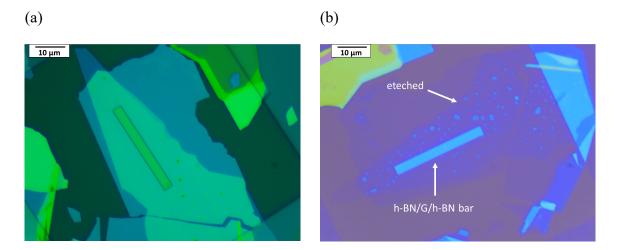

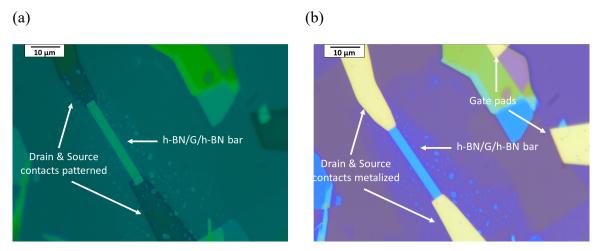

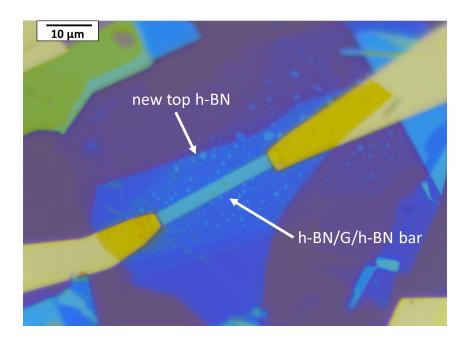

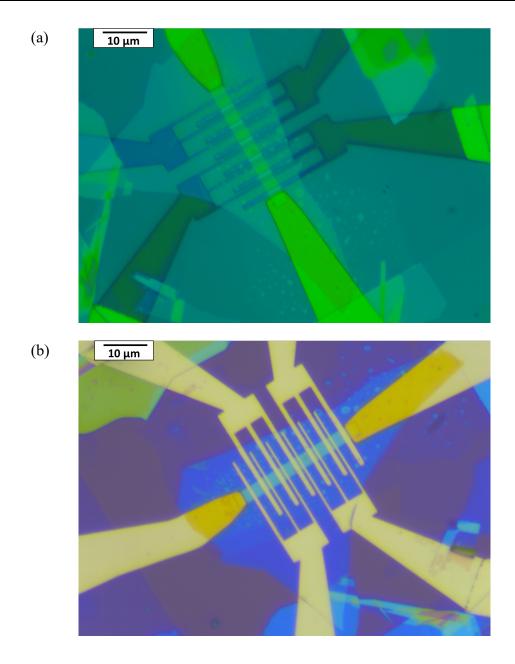

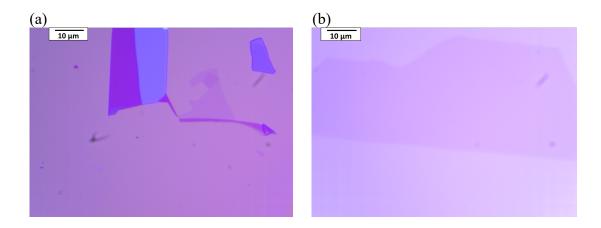

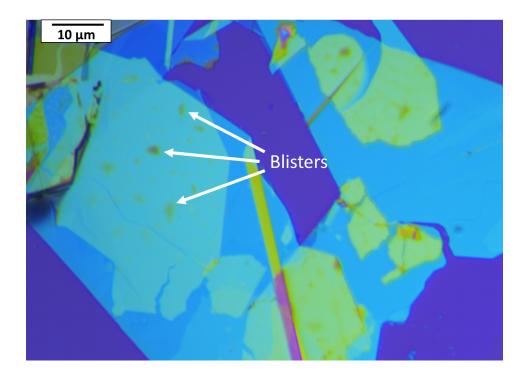

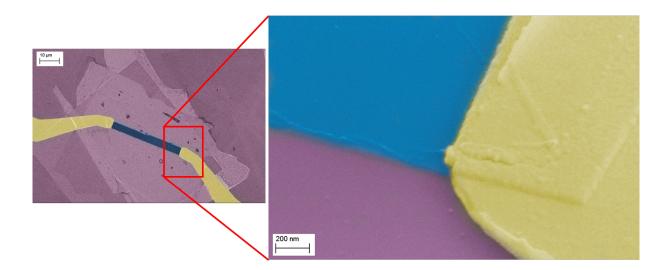

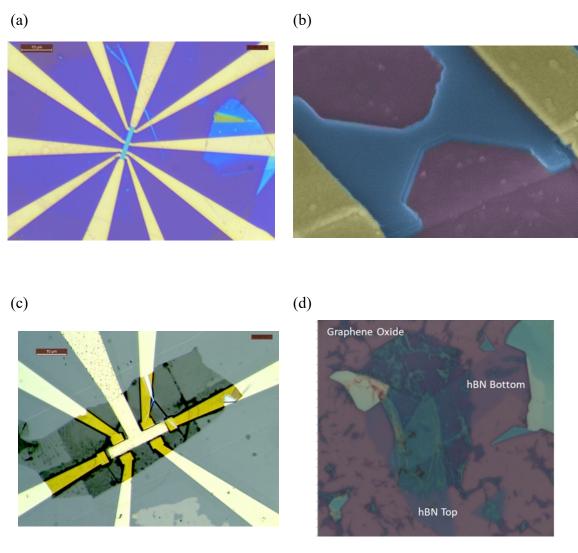

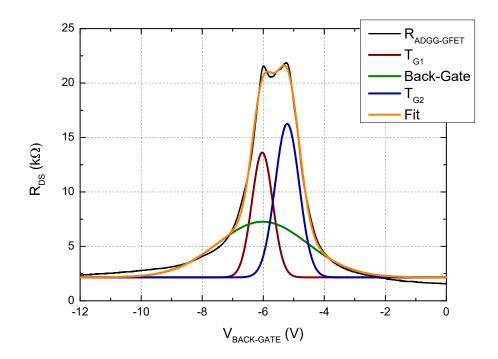

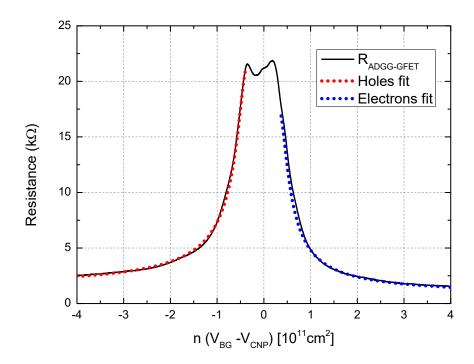

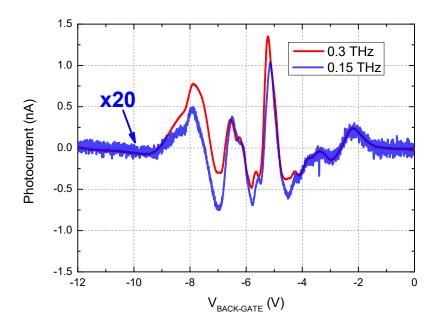

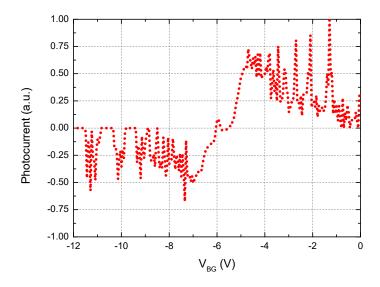

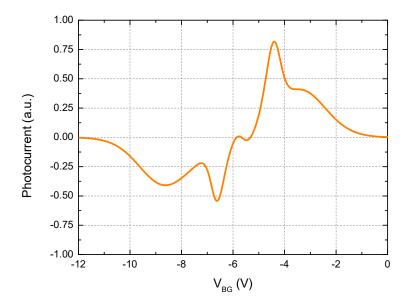

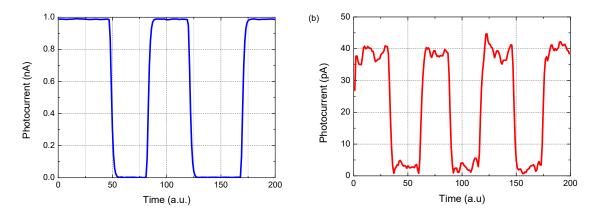

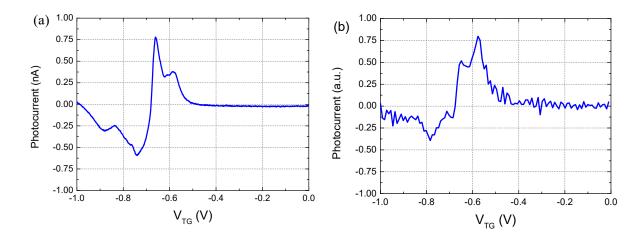

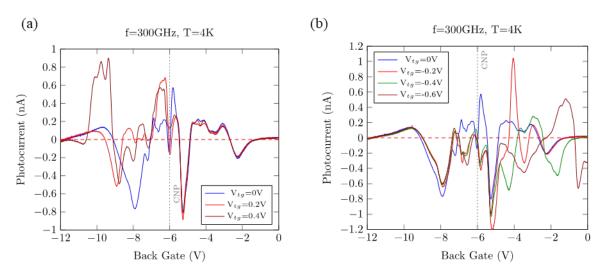

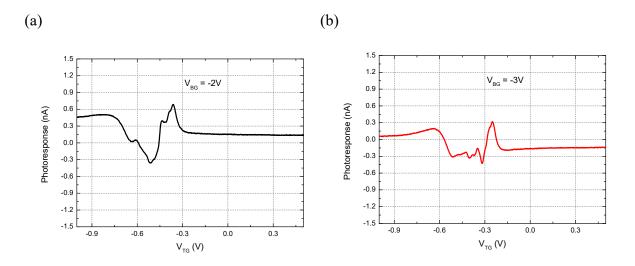

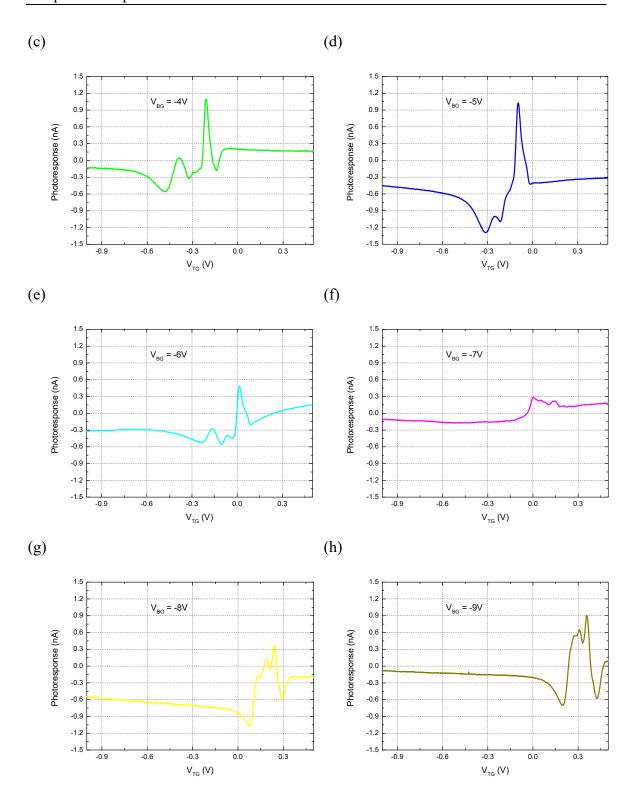

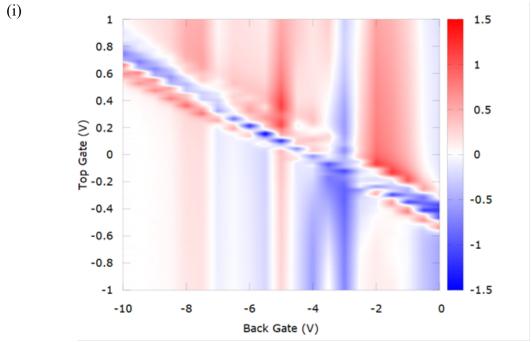

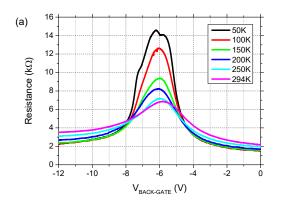

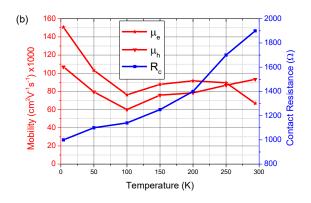

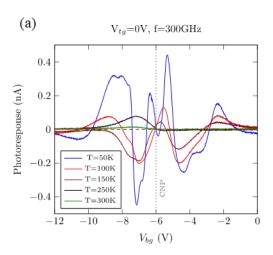

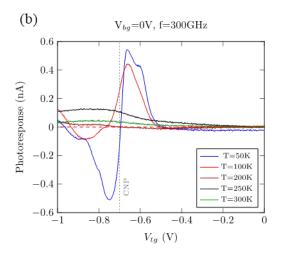

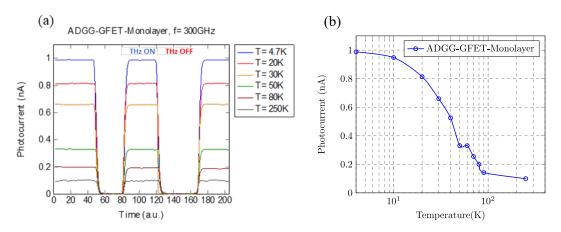

**Table 3.3** Default silicon parameters on the mobility concentration model